Intel BOXD865GLCL Product Specification - Page 19

Table 4., Specifications - corporation

|

UPC - 735858159869

View all Intel BOXD865GLCL manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 19 highlights

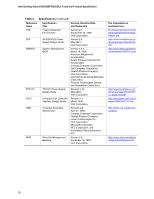

Product Description Table 4. Specifications (continued) Reference Name DDR SDRAM EHCI EPP El Torito LPC MicroATX PCI Plug and Play Specification Title Double Data Rate (DDR) SDRAM Specification Design Specification for a 184 Pin DDR Unbuffered DIMM Intel ® JEDEC DDR 200/266 Unbuffered DIMM Specification Addendum Enhanced Host Controller Interface Specification for Universal Serial Bus IEEE Std 1284.1-1997 (Enhanced Parallel Port) Bootable CD-ROM Format Specification Low Pin Count Interface Specification microATX Motherboard Interface Specification PCI Local Bus Specification PCI Bus Power Management Interface Specification Plug and Play BIOS Specification Version, Revision Date and Ownership Version 1.0, June 2000, JEDEC Solid State Technology Association. Revision 1.0, October 2001, JEDEC Solid State Technology Association. Revision 0.9, September 27, 2001, Intel Corporation. Revision 1.0, March 12, 2002, Intel Corporation. Version 1.7, 1997, Institute of Electrical and Electronic Engineers. Version 1.0, January 25, 1995, Phoenix Technologies Limited and International Business Machines Corporation. Revision 1.0, September 29, 1997, Intel Corporation. Version 1.0, December 1997, Intel Corporation. Revision 2.2, December 18, 1998, PCI Special Interest Group. Revision 1.1, December 18, 1998, PCI Special Interest Group. Version 1.0a, May 5, 1994, Compaq Computer Corporation, Phoenix Technologies Limited, and Intel Corporation. The information is available from... http://www.jedec.org/ http://www.jedec.org/ http://developer.intel.com/t echnology/memory/index.ht m http://developer.intel.com/t echnology/usb/download/e hci-r10.pdf http://standards.ieee.org/re ading/ieee/std_public/descr iption/busarch/1284.11997_desc.html http://www.phoenix.com/Pl atSS/products/specs.html http://www.intel.com/design /chipsets/industry/lpc.htm http://www.formfactors.org/ developer/specs/microatx/ microatxspecs.htm http://www.pcisig.com/speci fications http://www.pcisig.com/speci fications http://www.microsoft.com/h wdev/tech/PnP/default.asp continued 19