MSI 790XT User Guide - Page 71

De-29, Deutsch

|

View all MSI 790XT manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 71 highlights

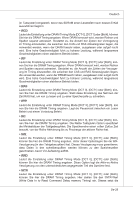

Deutsch (in Taktzyklen) eingestellt, bevor das SDRAM einen Lesebefehl nach dessen Erhält auszuführen beginnt. ▶ tRCD Lautet die Einstellung unter DRAM Timing Mode [DCT 0], [DCT1] oder [Both], können Sie hier die DRAM Timing angeben. Wenn DRAM erneuert wird, werden Reihen und Spalten separat adressiert. Gestattet es, die Anzahl der Zyklen der Verzogerung im Timing einzustellen, die zwischen den CAS und RAS Abtastsignalen liegen, die verwendet werden, wenn der DRAM beschr ieben, ausgelesen oder aufgef rischt wird. Eine hohe Geschwindigkeit fuhrt zu hoherer Leistung, während langsamere Geschwindigkeiten einen stabileren Betrieb bieten. ▶ tRP Lautet die Einstellung unter DRAM Timing Mode [DCT 0], [DCT1] oder [Both], können Sie hier die DRAM Timing angeben. Wenn DRAM erneuert wird, werden Reihen und Spalten separat adressiert. Gestattet es, die Anzahl der Zyklen der Verzogerung im Timing einzustellen, die zwischen den CAS und RAS Abtastsignalen liegen, die verwendet werden, wenn der DRAM beschr ieben, ausgelesen oder aufgef rischt wird. Eine hohe Geschwindigkeit fuhrt zu hoherer Leistung, während langsamere Geschwindigkeiten einen stabileren Betrieb bieten. ▶ tRAS Lautet die Einstellung unter DRAM Timing Mode [DCT 0], [DCT1] oder [Both], können Sie hier die DRAM Timing angeben. Stellt diese Einstellung das Nehmen der Zeit RAS fest, um von zu lesen und zu einer Speicherzelle zu schreiben. ▶ tRTP Lautet die Einstellung unter DRAM Timing Mode [DCT 0], [DCT1] oder [Both], kön nen Sie hier die DRAM Timing angeben. Legt die Pausenzeit zwischen ein Lesen Befehl und einem Vorladung Befehl. ▶ tRC Lautet die Einstellung unter DRAM Timing Mode [DCT 0], [DCT1] oder [Both], können Sie hier die DRAM Timing angeben. Die Reihe Taktzyklen Option spezifiziert die Mindestdauer der Taktgeberzyklen. Die Speicherreihe einen vollen Zyklus Zeit braucht, von der Reihe Aktivierung bis zu Precharge der aktiven Reihe fest. ▶ tWR Lautet die Einstellung unter DRAM Timing Mode [DCT 0], [DCT1] oder [Both], können Sie hier die DRAM Timing angeben. Unter dieser Optionlegen Sie die WRVerzögerung (in den Taktgeberzyklen) fest. Dieses Verzögerung muss garantieren, dass Daten in den schreibenpuffern werden können zu den Speicherzellen geschrieben, bevor Vor-Aufladung auftritt. ▶ tRRD Lautet die Einstellung unter DRAM Timing Mode [DCT 0], [DCT1] oder [Both], können Sie hier die DRAM Timing angeben. Diese Option legt die Aktiv-zu-Aktive Verzögerung von den unterschiedlichen angegrenzter Teil des Speicher fest. ▶ tWTR Lautet die Einstellung unter DRAM Timing Mode [DCT 0], [DCT1] oder [Both], können Sie hier die DRAM Timing angeben. Hier stellen Sie den tWTR-Wert (Write Data In to Read Command Delay memory Timing) ein. Dieses setzt die De-29