Sony PCV-J100 Reference Manual - Page 88

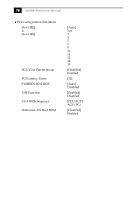

SDRAM RAS to CAS Delay, Memory Hole At 15M-16M

|

View all Sony PCV-J100 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 88 highlights

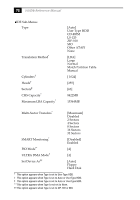

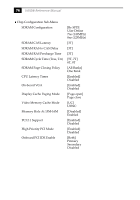

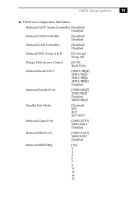

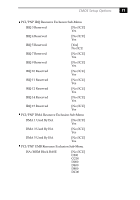

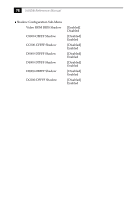

74 VAIO® Reference Manual Chip Configuration Sub-Menu SDRAM Configuration SDRAM CAS Latency SDRAM RAS to CAS Delay SDRAM RAS Precharge Time SDRAM Cycle Time (Tras, Trc) SDRAM Page Closing Policy CPU Latency Timer On-board VGA Display Cache Paging Mode Video Memory Cache Mode Memory Hole At 15M-16M PCI 2.1 Support High Priority PCI Mode Onboard PCI IDE Enable [By SPD] User Define 7ns (143MHz) 8ns (125MHz) [3T] [3T] [3T] [5T, 7T] 6T, 8T [All Banks] One Bank [Enabled] Disabled [Enabled] Disabled [Page open] Page close [UC] USWC [Disabled] Enabled [Enabled] Disabled [Enabled] Disabled [Both] Primary Secondary Disabled

VAIO

®

Reference Manual

74

Chip Configuration Sub-Menu

SDRAM Configuration

[By SPD]

User Define

7ns (143MHz)

8ns (125MHz)

SDRAM CAS Latency

[3T]

SDRAM RAS to CAS Delay

[3T]

SDRAM RAS Precharge Time

[3T]

SDRAM Cycle Time (Tras, Trc)

[5T, 7T]

6T, 8T

SDRAM Page Closing Policy

[All Banks]

One Bank

CPU Latency Timer

[Enabled]

Disabled

On-board VGA

[Enabled]

Disabled

Display Cache Paging Mode

[Page open]

Page close

Video Memory Cache Mode

[UC]

USWC

Memory Hole At 15M-16M

[Disabled]

Enabled

PCI 2.1 Support

[Enabled]

Disabled

High Priority PCI Mode

[Enabled]

Disabled

Onboard PCI IDE Enable

[Both]

Primary

Secondary

Disabled