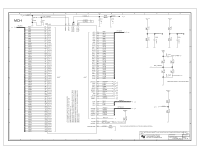

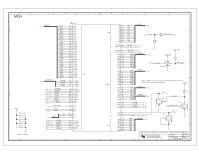

Intel VC820 Design Guide - Page 207

CPU TACH0, Single CPU0, Dual CPU

|

View all Intel VC820 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 207 highlights

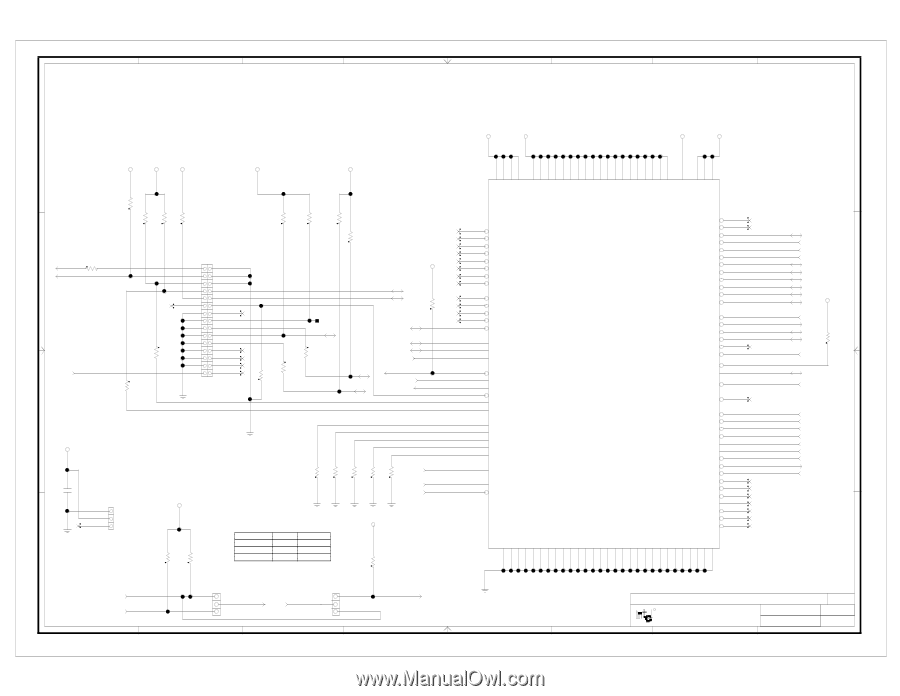

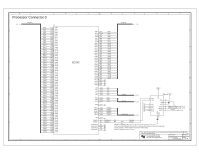

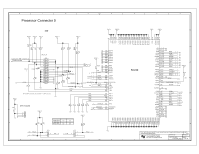

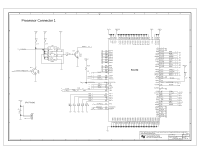

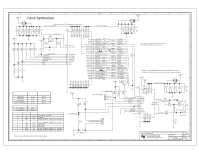

8 7 6 Processor Connector 0 D ITP VCC3_3 VCC2_5 VTT1_5 VCC2_5 5 VTT1_5 4 VTT1_5 VCCVID J15 R159 R17 240 1K R63 1K R18 1K R387 330 R76 330 R380 R218 150 150 R94 240 R386 240 R11 47 R7 47 ITP_PU_R 4,6,8CPURST# R95 CPURST#_R C 33 DBRESET# 240 TMS_R 6 TCK_R XREF=6 ITPCLK 7 J26 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 B VCC12 R7 and R11 should be placed within 1" of ITP connector. R93 680 TRST# 6 ITPREQ# 4 ITPRDY#_R ITPREQ1# 6 ITPRDY1#_R ITPPRDY# ITPRDY1# TCK 6 TMS R2 0K R1 0K 0.1UF CPU TACH0 C36 JP31 1 2 3 A VCC2_5 ITP Config Single CPU0 Dual CPU Single CPU1 JP33 1-2 2-3 2-3 JP34 1-2 1-2 2-3 R3 0K VCC3_3 TDI 4 TDO 4 R376 6 4 33 6 6,10,34 6,10,34 7 SLOTOCC0# 4 4,6 8.2K BINIT# PICD0 PICD1 PICCLK TDI_0 TDO_0 A25 DEP#0 A27 DEP#1 B26 DEP#2 A28 DEP#3 B27 DEP#4 A29 DEP#5 A31 DEP#6 B28 DEP#7 B19 BP2# A21 BP3# A23 BPM0# B24 BPM1# A24 BINIT# A19 PICD0 B22 PICD1 B18 PICCLK B101 A9 A11 B11 B7 B10 SLOTOCC# TDI TDO TRST# TCK TMS EMI1 EMI2 EMI3 EMI4 EMI5 B61 B100 B81 B1 B41 EMI_1 EMI_2 EMI_3 EMI_4 EMI_5 0K R4 6,7 6,33 4,6,8 CPUHCLK PWRGOOD CPURST# A75 BCLK A12 PWRGOOD B74 RESET# VCC2_5 0K 330 R5 R388 R92 150 R64 150 4,6 TDO_0 6 TDO_1 JP33 1 2 3 TDO 4 4 TDI JP34 1 2 3 TDI_0 4 8 7 6 5 4 GND29 A118 GND28 A114 GND27 A110 GND26 A106 GND25 A102 GND24 A98 GND23 A94 GND22 A90 GND21 A86 GND20 A82 GND19 A78 GND18 A74 GND17 A70 GND16 A66 GND15 A62 GND14 A58 GND13 A54 GND12 A50 GND11 A46 GND10 A42 GND9 A38 GND8 A34 GND7 A30 GND6 A26 GND5 A22 GND4 A18 GND2 A10 GND1 A6 GND0 A2 B121 VCC3_3 B117 VCC3_2 B113 VCC3_1 B109 VCC5 B105 VCCP19 B97 VCCP18 B93 VCCP17 B89 VCCP16 B85 VCCP15 B77 VCCP14 B73 VCCP13 B69 VCCP12 B65 VCCP11 B57 VCCP10 B53 VCCP9 B49 VCCP8 B45 VCCP7 B37 VCCP6 B33 VCCP5 B29 VCCP4 B25 VCCP3 B17 VCCP2 B13 VCCP1 B9 VTT4 B5 VTT3 A3 VTT2 A1 VTT1 3 2 VCC5 VCC3_3 1 D SC242 AP0# AP1# BNR# BPRI# TRDY# DEFER# LOCK# DRDY# HITM# HIT# DBSY# HADS# A117 B116 A101 A103 A104 A105 B106 B107 A109 B110 A111 A115 BNR# BPRI# HTRDY# DEFER# HLOCK# DRDY# HITM# HIT# DBSY# HADS# 6,8 6,8 6,8 6,8 6,8 6,8 6,8 C 6,8 6,8 VCC3_3 6,8 PREQ# A20 PRDY# B23 BREQ0# A76 BREQ1# B75 RES4 B76 TESTHI A13 BSEL0 BSEL1 B21 A14 FLUSH# B2 ITPREQ# ITPPRDY# BREQ#0 BREQ#1 TESTHI SEL133/100# FLUSH# 4 4 R375 6 6 220 34 6,7,9 6,34 THMTRP# A15 A20M# A5 A20M# STPCLK# B6 STPCLK# 6,10,34 B 6,10,34 SLP# B8 SLP# 6,10,34 SMI# B3 SMI# 6,10,34 LINT0 A17 LINT0 6,10,34 LINT1 B16 LINT1 6,10,34 INIT# B4 HINIT# 6,10,12,34 FERR# A7 FERR# 6,10,34 IGNNE# A8 IGNNE# 6,10,34 IERR# A4 BERR# A77 AERR# B118 RES0 A16 RES1 B20 RES2 B112 RES3 A113 A TITLE: INTEL(R) 820 CHIPSET DUAL PROCESSOR CUSTOMER REFERENCE BOARD REV: PROCESSOR CONNECTOR 3.03 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST REVISED: SHEET: 11-29-1999_14:45 4 OF 38 3 2 1