LG 50PW450 Service Manual - Page 20

Filre And Electrical Shock Hazards, When Servicing If Is

|

View all LG 50PW450 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 20 highlights

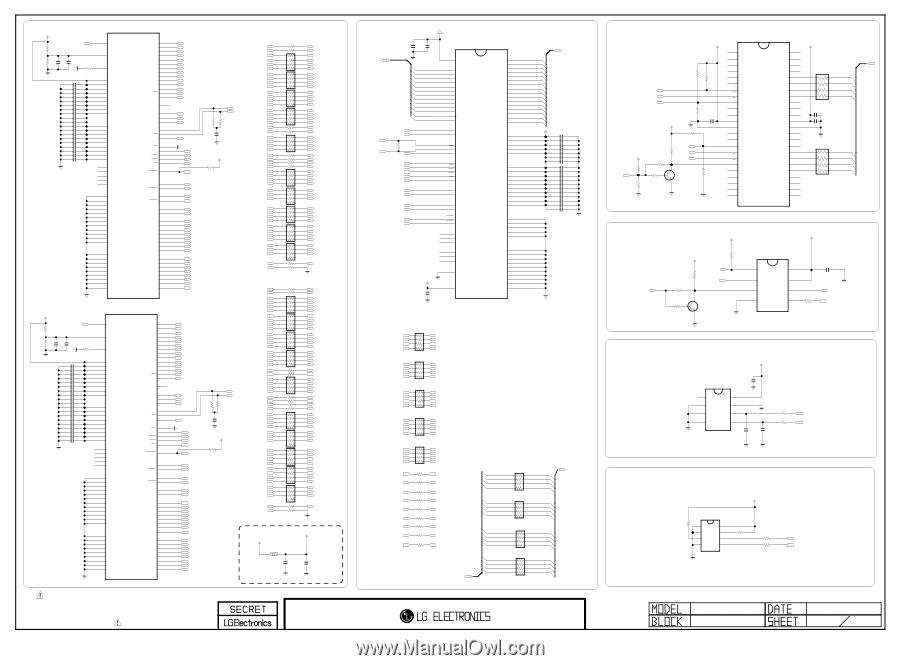

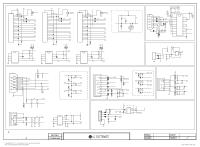

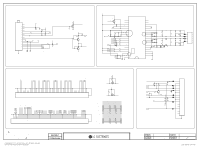

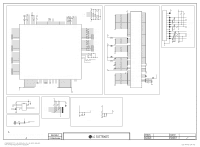

VCC_1.5V_DDR IC500 H5TQ1G63BFR-H9C R502 1K 1% R503 1K 1% A-MVREFCA M8 VREFCA A-MVREFDQ H1 VREFDQ C501 C503 0.1uF 1000pF R505 240 1% C524 C525 C526 C527 C528 C529 C530 C531 C532 C533 C505 C534 C535 C536 C537 C538 C539 C540 C541 10uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF L8 ZQ B2 VDD_1 D9 VDD_2 G7 VDD_3 K2 VDD_4 K8 VDD_5 N1 VDD_6 N9 VDD_7 R1 VDD_8 R9 VDD_9 A1 VDDQ_1 A8 VDDQ_2 C1 VDDQ_3 C9 VDDQ_4 D2 VDDQ_5 E9 VDDQ_6 F1 VDDQ_7 H2 VDDQ_8 H9 VDDQ_9 J1 NC_1 J9 NC_2 L1 NC_3 L9 NC_4 T7 NC_6 A9 VSS_1 B3 VSS_2 E1 VSS_3 G8 VSS_4 J2 VSS_5 J8 VSS_6 M1 VSS_7 M9 VSS_8 P1 VSS_9 P9 VSS_10 T1 VSS_11 T9 VSS_12 B1 VSSQ_1 B9 VSSQ_2 D1 VSSQ_3 D8 VSSQ_4 E2 VSSQ_5 E8 VSSQ_6 F9 VSSQ_7 G1 VSSQ_8 G9 VSSQ_9 N3 A0 P7 A1 P3 A2 N2 A3 P8 A4 P2 A5 R8 A6 R2 A7 T8 A8 R3 A9 L7 A10/AP R7 A11 N7 A12/BC T3 A13 M7 A15 M2 BA0 N8 BA1 M3 BA2 J7 CK K7 CK K9 CKE L2 CS K1 ODT J3 RAS K3 CAS L3 WE T2 RESET F3 DQSL G3 DQSL C7 DQSU B7 DQSU E7 DML D3 DMU E3 DQL0 F7 DQL1 F2 DQL2 F8 DQL3 H3 DQL4 H8 DQL5 G2 DQL6 H7 DQL7 D7 DQU0 C3 DQU1 C8 DQU2 C2 DQU3 A7 DQU4 A2 DQU5 B8 DQU6 A3 DQU7 VCC_1.5V_DDR R500 1K 1% R501 1K 1% B-MVREFCA B-MVREFDQ C500 C502 0.1uF 1000pF R504 240 1% C506 C507 C508 C509 C510 C511 C512 C513 C514 C515 C504 C516 C517 C518 C519 C520 C521 C522 C523 10uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF IC501 H5TQ1G63BFR-H9C M8 VREFCA H1 VREFDQ L8 ZQ B2 VDD_1 D9 VDD_2 G7 VDD_3 K2 VDD_4 K8 VDD_5 N1 VDD_6 N9 VDD_7 R1 VDD_8 R9 VDD_9 A1 VDDQ_1 A8 VDDQ_2 C1 VDDQ_3 C9 VDDQ_4 D2 VDDQ_5 E9 VDDQ_6 F1 VDDQ_7 H2 VDDQ_8 H9 VDDQ_9 J1 NC_1 J9 NC_2 L1 NC_3 L9 NC_4 T7 NC_6 A9 VSS_1 B3 VSS_2 E1 VSS_3 G8 VSS_4 J2 VSS_5 J8 VSS_6 M1 VSS_7 M9 VSS_8 P1 VSS_9 P9 VSS_10 T1 VSS_11 T9 VSS_12 B1 VSSQ_1 B9 VSSQ_2 D1 VSSQ_3 D8 VSSQ_4 E2 VSSQ_5 E8 VSSQ_6 F9 VSSQ_7 G1 VSSQ_8 G9 VSSQ_9 N3 A0 P7 A1 P3 A2 N2 A3 P8 A4 P2 A5 R8 A6 R2 A7 T8 A8 R3 A9 L7 A10/AP R7 A11 N7 A12/BC T3 A13 M7 A15 M2 BA0 N8 BA1 M3 BA2 J7 CK K7 CK K9 CKE L2 CS K1 ODT J3 RAS K3 CAS L3 WE T2 RESET F3 DQSL G3 DQSL C7 DQSU B7 DQSU E7 DML D3 DMU E3 DQL0 F7 DQL1 F2 DQL2 F8 DQL3 H3 DQL4 H8 DQL5 G2 DQL6 H7 DQL7 D7 DQU0 C3 DQU1 C8 DQU2 C2 DQU3 A7 DQU4 A2 DQU5 B8 DQU6 A3 DQU7 DDR3 Memory 1GBit x 2 A-MA0 A-MA1 A-MA2 A-MA3 A-MA4 A-MA5 A-MA6 A-MA7 A-MA8 A-MA9 A-MA10 A-MA11 A-MA12 A-MA13 A-MBA0 A-MBA1 A-MBA2 A-MCKE R509 56 1% R511 56 1% C543 0.01uF 50V A-MODT A-MRASB VCC_1.5V_DDR A-MCASB A-MWEB R506 10K A-MRESETB A-MDQSL A-MDQSLB A-MDQSU A-MDQSUB A-MA0 A-MA2 A-MA11 A-MA1 A-MA8 A-MA6 A-MBA0 A-MA3 A-MA5 A-MA7 A-MCK A-MCKB A-MA4 A-MA12 A-MBA1 A-MA10 A-MRESETB A-MBA2 A-MA13 A-MA9 A-MCK A-MCKB A-MRASB A-MCASB A-MODT A-MWEB A-MDQSL A-MDQSLB A-MDQSU A-MDQSUB A-MDQL1 A-MDQL3 A-MDML A-MDQU2 A-MCKE A-MDQL7 A-MDQL5 A-MDML A-MDMU A-MDQL0 A-MDQL1 A-MDQL2 A-MDQL3 A-MDQL4 A-MDQL5 A-MDQL6 A-MDQL7 A-MDQU0 A-MDQU1 A-MDQU2 A-MDQU3 A-MDQU4 A-MDQU5 A-MDQU6 A-MDQU7 A-MDQL0 A-MDQL2 A-MDQL6 A-MDQL4 A-MDQU7 A-MDQU3 A-MDQU5 A-MDMU A-MDQU6 A-MDQU0 A-MDQU4 A-MDQU1 A-MCKE B-MA0 B-MA2 B-MA0 B-MA1 B-MA2 B-MA3 B-MA4 B-MA5 B-MA6 B-MA7 B-MA8 B-MA9 B-MA10 B-MA11 B-MA12 B-MA13 B-MBA0 B-MBA1 B-MBA2 R508 56 1% R510 56 1% B-MCK B-MCKB B-MA11 B-MA1 B-MA8 B-MA6 B-MBA0 B-MA3 B-MA5 B-MA7 B-MA4 B-MA12 B-MBA1 B-MA10 B-MRESETB B-MBA2 B-MA13 B-MA9 B-MCK B-MCKB B-MRASB B-MCASB B-MODT B-MWEB B-MDQSL B-MDQSLB B-MDQSU B-MDQSUB B-MCKE C542 0.01uF 50V B-MODT B-MRASB B-MCASB B-MWEB VCC_1.5V_DDR R507 10K B-MRESETB B-MDQSL B-MDQSLB B-MDQSU B-MDQSUB B-MDML B-MDMU B-MDQL1 B-MDQL3 B-MDML B-MDQU2 B-MCKE B-MDQL7 B-MDQL5 B-MDQL0 B-MDQL2 B-MDQL6 B-MDQL4 B-MDQU7 B-MDQU3 B-MDQU5 B-MDMU B-MDQU6 B-MDQU0 B-MDQU4 R513 R514 AR500 AR501 AR502 AR503 R515 R516 AR504 R517 R518 R519 R520 AR505 AR506 AR507 AR508 AR509 R521 R512 R522 R523 AR510 AR511 AR512 AR513 R524 R525 AR514 R526 R527 R528 R529 AR515 AR516 AR517 AR518 AR519 56 56 56 56 56 56 22 22 56 22 22 22 22 22 22 22 22 22 22 10K A-TMA0 A-TMA2 A-TMA11 A-TMA1 A-TMA8 A-TMA6 A-TMBA0 A-TMA3 A-TMA5 A-TMA7 A-TMA4 A-TMA12 A-TMBA1 A-TMA10 A-TMRESETB A-TMBA2 A-TMA13 A-TMA9 A-TMCK A-TMCKB A-TMRASB A-TMCASB A-TMODT A-TMWEB A-TMDQSL A-TMDQSLB A-TMDQSU A-TMDQSUB A-TMDQL1 A-TMDQL3 A-TMDML A-TMDQU2 A-TMCKE A-TMDQL7 A-TMDQL5 A-TMDQL0 A-TMDQL2 A-TMDQL6 A-TMDQL4 A-TMDQU7 A-TMDQU3 A-TMDQU5 A-TMDMU A-TMDQU6 A-TMDQU0 A-TMDQU4 A-TMDQU1 56 B-TMA0 56 B-TMA2 56 B-TMA11 B-TMA1 B-TMA8 B-TMA6 56 B-TMBA0 B-TMA3 B-TMA5 B-TMA7 56 B-TMA4 B-TMA12 B-TMBA1 B-TMA10 56 B-TMRESETB B-TMBA2 B-TMA13 B-TMA9 22 B-TMCK 22 B-TMCKB 56 B-TMRASB B-TMCASB B-TMODT B-TMWEB 22 B-TMDQSL 22 B-TMDQSLB 22 B-TMDQSU 22 B-TMDQSUB 22 B-TMDQL1 B-TMDQL3 B-TMDML B-TMDQU2 22 B-TMCKE B-TMDQL7 B-TMDQL5 22 B-TMDQL0 B-TMDQL2 B-TMDQL6 B-TMDQL4 22 B-TMDQU7 B-TMDQU3 B-TMDQU5 B-TMDMU 22 B-TMDQU6 B-TMDQU0 B-TMDQU4 B-MDQL0 B-MDQL1 B-MDQL2 B-MDQL3 B-MDQL4 B-MDQL5 B-MDQL6 B-MDQL7 B-MDQU0 B-MDQU1 B-MDQU2 B-MDQU3 B-MDQU4 B-MDQU5 B-MDQU6 B-MDQU7 B-MDQU1 B-MCKE R530 R531 22 10K B-TMDQU1 +1.5V_DDR_IN VCC_1.5V_DDR L500 500 Main C544 10uF 10V C545 0.1uF 16V THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION. FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC. Copyright © 2011 LG Electronics Inc. All rights reserved. Only for training and service purposes DDR_A[12-0] DDR2_CLK DDR_BA[0] DDR_BA[1] 3D R700 100 /DDR2_CLK DDR2_CKE DDR2_ODT /DDR_CS /DDR_RAS /DDR_CAS /DDR_WE DDR_DQS0P DDR_DQS1P DDR_DQM0 DDR_DQM1 DDR_DQS0M DDR_DQS1M DDR_VREF_DDR 3D C702 0.1uF 16V 3D C704 470pF 50V LG8300 DDR3 256MBit IC701 W9725G6JB-25 Memory DDR_DQ[15-0] DDR_A[0] DDR_A[1] DDR_A[2] DDR_A[3] DDR_A[4] DDR_A[5] DDR_A[6] DDR_A[7] DDR_A[8] DDR_A[9] DDR_A[10] DDR_A[11] DDR_A[12] VREF J2 A0 M8 A1 M3 A2 M7 A3 N2 A4 N8 A5 N3 A6 N7 A7 P2 A8 P8 A9 P3 A10/AP M2 A11 P7 A12 R2 G8 DQ0 G2 DQ1 H7 DQ2 H3 DQ3 H1 DQ4 H9 DQ5 F1 DQ6 F9 DQ7 C8 DQ8 C2 DQ9 D7 DQ10 D3 DQ11 D1 DQ12 D9 DQ13 B1 DQ14 B9 DQ15 DDR_DQ[0] DDR_DQ[1] DDR_DQ[2] DDR_DQ[3] DDR_DQ[4] DDR_DQ[5] DDR_DQ[6] DDR_DQ[7] DDR_DQ[8] DDR_DQ[9] DDR_DQ[10] DDR_DQ[11] DDR_DQ[12] DDR_DQ[13] DDR_DQ[14] DDR_DQ[15] BA0 L2 BA1 L3 CLK J8 CLK K8 CKE K2 ODT K9 CS L8 RAS K7 CAS L7 WE K3 LDQS F7 UDQS B7 LDM F3 UDM B3 A1 VDD_5 E1 VDD_4 J9 VDD_3 M9 VDD_2 R1 VDD_1 A9 VDDQ_10 C1 VDDQ_9 C3 VDDQ_8 C7 VDDQ_7 C9 VDDQ_6 E9 VDDQ_5 G1 VDDQ_4 G3 VDDQ_3 G7 VDDQ_2 G9 VDDQ_1 +1.8V C720 0.1uF 3D C719 0.1uF 3D C718 0.1uF 3D C717 0.1uF 3D C716 0.1uF 3D C715 0.1uF 3D C714 0.1uF 3D C713 0.1uF 3D C712 0.1uF 3D C711 0.1uF 3D C710 0.1uF 3D C709 0.1uF 3D C708 0.1uF 3D C707 0.1uF 3D C706 0.1uF 3D C703 0.1uF 3D C701 0.1uF 3D C700 10uF 3D +1.8V 3D C705 100pF 50V LDQS E8 UDQS A8 NC_4 L1 NC_5 R3 NC_6 R7 NC_1 A2 NC_2 E2 NC_3 R8 VSSDL J7 VDDL J1 A3 VSS_5 E3 VSS_4 J3 VSS_3 N1 VSS_2 P9 VSS_1 B2 VSSQ_10 B8 VSSQ_9 A7 VSSQ_8 D2 VSSQ_7 D8 VSSQ_6 E7 VSSQ_5 F2 VSSQ_4 F8 VSSQ_3 H2 VSSQ_2 H8 VSSQ_1 /C_DDR_WE C_DDR2_CKE C_DDR_BA[1] C_DDR_BA[0] AR531 3D 22 1/16W AR532 3D 22 1/16W C_DDR_A[2] C_DDR_A[0] /C_DDR_RAS C_DDR2_ODT AR533 3D 22 1/16W C_DDR_A[1] C_DDR_A[3] C_DDR_A[12] C_DDR_A[9] C_DDR_A[10] C_DDR_A[5] C_DDR_A[7] C_DDR_A[11] AR534 3D 22 1/16W C_DDR_A[8] C_DDR_A[6] C_DDR_A[4] /C_DDR_CAS AR535 3D 22 1/16W C_DDR2_CLK /C_DDR2_CLK C_DDR_DQS0P C_DDR_DQS1P C_DDR_DQM0 C_DDR_DQM1 C_DDR_DQS0M C_DDR_DQS1M /C_DDR_CS R1459 3D 22 R1460 3D 22 R1461 3D 22 R1462 3D 22 R1463 3D 22 R1464 3D 22 R1465 3D 22 R1466 3D 22 R1467 3D 22 /DDR_WE DDR2_CKE DDR_BA[1] DDR_BA[0] DDR_A[2] DDR_A[0] /DDR_RAS DDR2_ODT DDR_A[1] DDR_A[3] DDR_A[12] DDR_A[9] DDR_A[10] DDR_A[5] DDR_A[7] DDR_A[11] DDR_A[8] DDR_A[6] DDR_A[4] /DDR_CAS DDR2_CLK /DDR2_CLK DDR_DQS0P DDR_DQS1P DDR_DQM0 DDR_DQM1 DDR_DQS0M DDR_DQS1M /DDR_CS C_DDR_DQ[5] 3D C_DDR_DQ[2] AR527 22 1/16W C_DDR_DQ[0] C_DDR_DQ[7] AR528 22 1/16W C_DDR_DQ[13] 3D C_DDR_DQ[10] C_DDR_DQ[8] C_DDR_DQ[15] C_DDR_DQ[14] 3D C_DDR_DQ[9] AR529 22 1/16W C_DDR_DQ[11] C_DDR_DQ[12] C_DDR_DQ[3] 3D C_DDR_DQ[4] C_DDR_DQ[1] C_DDR_DQ[6] AR530 22 1/16W C_DDR_DQ[15-0] DDR_DQ[15-0] DDR_DQ[5] DDR_DQ[2] DDR_DQ[0] DDR_DQ[7] DDR_DQ[13] DDR_DQ[10] DDR_DQ[8] DDR_DQ[15] DDR_DQ[14] DDR_DQ[9] DDR_DQ[11] DDR_DQ[12] DDR_DQ[3] DDR_DQ[4] DDR_DQ[1] DDR_DQ[6] NAND Flash 1GBit R537 1K /F_RB /PF_OE /PF_CE0 READY R538 1K +3.3V_AVDD /PF_WP READY R541 1K +3.3V_ST R532 3.3K READY R533 3.3K R536 10K READY /PF_CE1 PF_ALE R535 0 /PF_WE B R534 10K READY C Q500 2SC3052 READY E R542 1K +3.3V_AVDD IC502 H27U1G8F2BTR-BC +3.3V_AVDD R545 4.7K C549 0.1uF NC_1 1 NC_2 2 NC_3 3 NC_4 4 NC_5 5 NC_6 6 R/B 7 RE 8 CE 9 NC_7 10 NC_8 11 VCC_1 12 VSS_1 13 NC_9 14 NC_10 15 CLE 16 ALE 17 WE 18 WP 19 NC_11 20 NC_12 21 NC_13 22 NC_14 23 NC_15 24 NC_29 48 NC_28 47 NC_27 46 NC_26 45 I/O7 44 I/O6 43 I/O5 42 I/O4 41 NC_25 40 NC_24 39 NC_23 38 VCC_2 37 VSS_2 36 NC_22 35 NC_21 34 NC_20 33 I/O3 32 I/O2 31 I/O1 30 I/O0 29 NC_19 28 NC_18 27 NC_17 26 NC_16 25 AR520 PCM_A[7] PCM_A[6] PCM_A[5] PCM_A[4] 22 C550 10uF C551 0.1uF AR521 PCM_A[3] PCM_A[2] PCM_A[1] PCM_A[0] 22 PCM_A[0-7] SERIAL FLASH 8MBit +3.3V_ST +3.3V_ST /FLASH_WP +3.3V_ST R547 4.7K READY R546 10K R540 0 /SPI_CS SPI_SDO B R539 10K READY C READY Q501 2SC3052 E IC503 MX25L8005M2I-15G CS# 1 SO 2 WP# 3 GND 4 VCC 8 HOLD# 7 SCLK 6 SI 5 R549 33 C552 0.1uF SPI_SCK SPI_SDI EEPROM 1MBit +3.3V_AVDD IC504 M24M01-HRMN6TP C547 0.1uF NC 1 E1 2 E2 3 VSS 4 VCC 8 WP 7 SCL 6 SDA 5 C546 10pF READY R543 R544 C548 10pF READY 22 I2C_SCL 22 I2C_SDA A0'h HDCP EEPROM 8KBit +3.3V_AVDD R548 4.7K IC505 CAT24WC08W-T A0 1 A1 2 A2 3 VSS 4 8 VCC 7 WP R550 6 SCL 5 SDA 4.7K R551 22 R552 22 I2C_SCL I2C_SDA Addr:10101-- GP2R_S7R Memory 2010-08-31 5 LGE Internal Use Only