LG 50PW450 Service Manual - Page 22

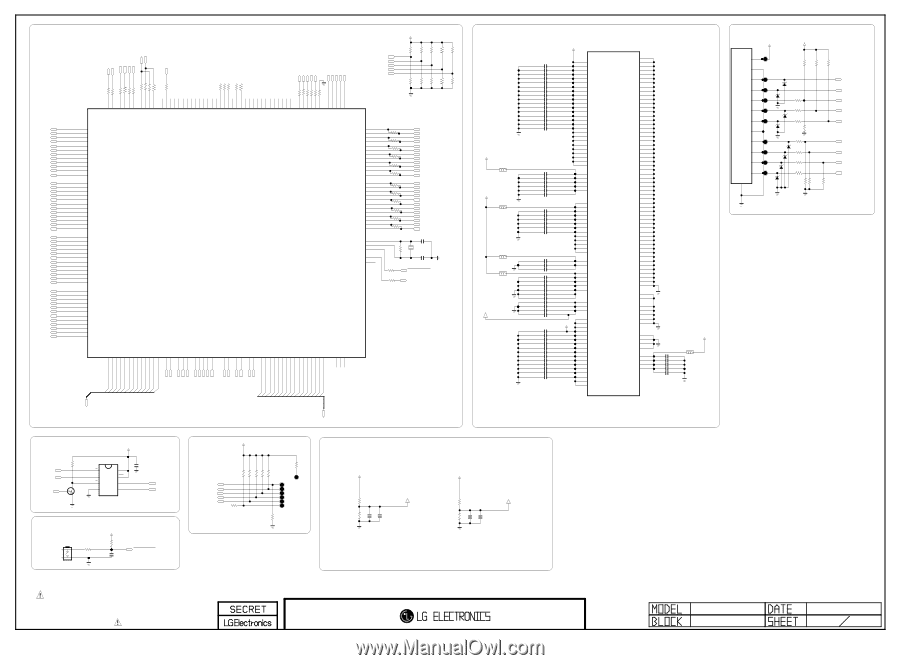

IC700, LG8300

|

View all LG 50PW450 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 22 highlights

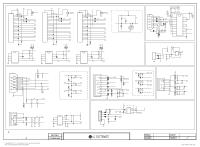

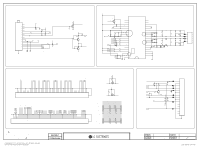

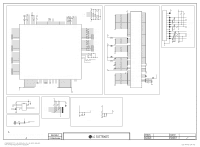

TE4P TE4N TD4P TD4N TCLK4P TCLK4N TC4P TC4N TB4P TB4N TA4P TA4N TE3P TE3N TD3P TD3N TCLK3P TCLK3N TC3P TC3N TB3P TB3N TA3P TA3N TE2P TE2N TD2P TD2N TCLK2P TCLK2N TC2P TC2N TB2P TB2N TA2P TA2N TE1P TE1N TD1P TD1N TCLK1P TCLK1N TC1P TC1N TB1P TB1N TA1P TA1N B2 TE4P B1 TE4N B3 TD4P C3 TD4N C1 TCLK4P C2 TCLK4N D2 TC4P D1 TC4N D3 TB4P E3 TB4N E1 TA4P E2 TA4N F2 TE3P F1 TE3N F3 TD3P G3 TD3N G1 TCLK3P G2 TCLK3N H2 TC3P H1 TC3N H3 TB3P J3 TB3N J1 TA3P J2 TA3N K2 TE2P K1 TE2N K3 TD2P L3 TD2N L1 TCLK2P L2 TCLK2N M2 TC2P M1 TC2N M3 TB2P N3 TB2N N1 TA2P N2 TA2N P2 TE1P P1 TE1N P3 TD1P R3 TD1N R1 TCLK1P R2 TCLK1N T2 TC1P T1 TC1N T3 TB1P U3 TB1N U1 TA1P U2 TA1N C_DDR_A[0] U5 C_DDR_A[1] V8 C_DDR_A[2] V5 C_DDR_A[3] U8 C_DDR_A[4] R6 C_DDR_A[5] T8 C_DDR_A[6] T6 C_DDR_A[7] R8 C_DDR_A[8] R7 C_DDR_A[9] U7 C_DDR_A[10] R9 C_DDR_A[11] T7 C_DDR_A[12] V7 DDR_ADDR[0] DDR_ADDR[1] DDR_ADDR[2] DDR_ADDR[3] DDR_ADDR[4] DDR_ADDR[5] DDR_ADDR[6] DDR_ADDR[7] DDR_ADDR[8] DDR_ADDR[9] DDR_ADDR[10] DDR_ADDR[11] DDR_ADDR[12] UART_TXD UART_RXD A16 B16 SPI_CS SPI_SCLK SPI_DO SPI_DI C16 D16 A15 B15 22 R1449 22 R1448 22 R905 22 R902 22 R903 22 R904 22 R1443 22 R1444 22 R1445 22 R1446 UART_TXD_3D UART_RXD_3D SPI_CSZ SPI_CK SPI_DI SPI_DO P_SCL P_SDA SCL SDA SCL_M SDA_M C15 D15 A14 B14 U9 DDR_BA[0] T9 DDR_BA[1] V6 DDR_CK U6 DDR_CK_N V9 DDR_CKE R5 U4 V4 T5 R10 GPIO[0] GPIO[1] GPIO[2] GPIO[3] GPIO[4] GPIO[5] GPIO[6] GPIO[7] GPIO[8] GPIO[9] GPIO[10] GPIO[11] GPIO[12] GPIO[13] GPIO[14] GPIO[15] GPIO[16] GPIO[17] GPIO[18] GPIO[19] GPIO[20] GPIO[21] GPIO[22] GPIO[23] GPIO[24] GPIO[25] GPIO[26] GPIO[27] GPIO[28] GPIO[29] GPIO[30] GPIO[31] TDI TMS TRST TDO TCK TEST_SE TMODE[0] TMODE[1] TMODE[2] TMODE[3] BOOT_SEL C14 D14 A13 B13 C13 D13 A12 B12 C12 D12 A11 B11 C11 D11 A10 B10 C10 D10 A9 B9 C9 D9 A8 B8 C8 D8 A7 B7 C7 D7 A6 B6 C6 D6 A5 B5 C5 D5 A4 B4 C4 D4 A3 R708 0 R721 0 R722 0 R723 0 R725 0 R726 0 22 R907 22 R908 22 R909 22 R910 22 R911 4.7K R739 FLASH_WP L/R_DETECT JTAG_TDI JTAG_TMS /JTAG_TRST JTAG_TDO JTAG_TCLK TMODE[0] TMODE[1] TMODE[2] TMODE[3] BOOT_SEL DDR_CS_N DDR_ODT DDR_RAS_N DDR_CAS_N DDR_WE_N V14 V12 IC700 LG8300 DDR_DQS[0] DDR_DQS[1] U14 U12 DDR_DQS_N[0] DDR_DQS_N[1] R15 T12 C_DDR_DQ[0] V15 T15 U16 T16 R16 V16 T14 DDR_DM[0] DDR_DM[1] DDR_DQ[0] DDR_DQ[1] DDR_DQ[2] DDR_DQ[3] DDR_DQ[4] DDR_DQ[5] DDR_DQ[6] DDR_DQ[7] DDR_DQ[8] DDR_DQ[9] DDR_DQ[10] DDR_DQ[11] DDR_DQ[12] DDR_DQ[13] DDR_DQ[14] DDR_DQ[15] U15 T13 V11 U10 T10 V10 DDR_TAOUT DDR_TDOUT[0] DDR_TDOUT[1] BOOT_SEL TMODE[3] TMODE[2] TMODE[1] TMODE[0] +3.3V_3D READY READY READY READY READY R745 R747 R749 R751 R753 3.3K 3.3K 3.3K 3.3K 3.3K R746 R748 R750 R752 R754 3.3K 3.3K 3.3K 3.3K 3.3K RA1N RA1P RB1N RB1P RC1N RC1P RCLK1N RCLK1P RD1N RD1P RE1N RE1P U18 U17 T18 T17 R18 R17 P18 P17 N18 N17 M18 M17 RA2N RA2P RB2N RB2P RC2N RC2P RCLK2N RCLK2P RD2N RD2P RE2N RE2P L18 L17 K18 K17 J18 J17 H18 H17 G18 G17 F18 F17 100 R1438 100 R1439 100 R896 R894 100 100 R891 R883 100 100 R878 R845 100 100 R895 R874 100 100 R840 R897 100 CLK_XIN CLK_XOUT PO_RST_N A17 B18 B17 V2 LR_SYNC V3 EMITTER_PULSE R1452 0 R1450 0 1M 1% R744 25MHz X700 50V 27pF C722 50V 27pF C721 LVDS_DATA_1_ALVDS_DATA_1_A+ LVDS_DATA_1_BLVDS_DATA_1_B+ LVDS_DATA_1_CLVDS_DATA_1_C+ LVDS_CLK_1LVDS_CLK_1+ LVDS_DATA_1_DLVDS_DATA_1_D+ LVDS_DATA_1_ELVDS_DATA_1_E+ LVDS_DATA_2_ALVDS_DATA_2_A+ LVDS_DATA_2_BLVDS_DATA_2_B+ LVDS_DATA_2_CLVDS_DATA_2_C+ LVDS_CLK_2LVDS_CLK_2+ LVDS_DATA_2_DLVDS_DATA_2_D+ LVDS_DATA_2_ELVDS_DATA_2_E+ LG8300_RESET 3D_L/R_SYNC +1.0V L704 BLM18PG121SN1D +3.3V_3D L705 BLM18PG121SN1D L712 BLM18PG121SN1D L706 BLM18PG121SN1D DDR_VREF_LG8300 +1.0V IC700 LG8300 C818 6.3V C791 6.3V C798 16V C756 16V C763 16V C770 16V C777 16V C781 16V C785 16V C790 16V C800 16V C808 16V C813 16V C757 16V C764 16V C771 16V 10uF 10uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF C820 6.3V C795 16V C803 16V C811 16V C828 16V C821 16V +1.0V_LTX 10uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF C794 6.3V C758 16V C765 16V C778 16V C772 16V C782 16V +3.3V_VDD 10uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF C832 6.3V C829 16V C831 16V C833 6.3V C796 16V C804 16V C812 16V C815 16V C816 16V C836 6.3V C835 16V C817 16V C837 16V +3.3V_LRX 10uF 0.1uF 0.1uF +3.3V_LTX 10uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 10uF 0.1uF 0.1uF 0.1uF C838 6.3V C792 6.3V C760 16V C767 16V C774 16V C779 16V C783 16V C787 16V C793 16V C802 16V C810 16V C814 16V 10uF 10uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF +1.8V F6 F13 G6 G7 G8 G9 G10 G11 G12 G13 H6 H13 J6 J13 K6 K13 L6 L7 L8 L9 L10 L11 L12 L13 M6 M13 H5 J5 K5 L5 M5 E5 E6 E7 E8 E9 E10 E11 E12 E13 E14 E15 F15 G15 L16 N16 E4 G4 L4 N4 J4 T4 R11 V17 N7 N8 N9 N10 N11 N12 N13 N14 P6 P7 P8 P9 P10 P12 P13 P14 P15 GND_0 VDD10_1 GND_1 VDD10_2 GND_2 VDD10_3 GND_3 VDD10_4 GND_4 VDD10_5 GND_5 VDD10_6 GND_6 VDD10_7 GND_7 VDD10_8 GND_8 VDD10_9 GND_9 VDD10_10 GND_10 VDD10_11 GND_11 VDD10_12 GND_12 VDD10_13 GND_13 VDD10_14 GND_14 VDD10_15 GND_15 VDD10_16 GND_16 VDD10_17 GND_17 VDD10_18 GND_18 VDD10_19 GND_19 VDD10_20 GND_20 VDD10_21 GND_21 VDD10_22 GND_22 VDD10_23 GND_23 VDD10_24 GND_24 VDD10_25 GND_25 VDD10_26 GND_26 GND_27 LTX_VDD10_1 GND_28 LTX_VDD10_2 GND_29 LTX_VDD10_3 GND_30 LTX_VDD10_4 GND_31 LTX_VDD10_5 GND_32 GND_33 GND_34 VDD33_1 GND_35 VDD33_2 GND_36 VDD33_3 GND_37 VDD33_4 GND_38 VDD33_5 GND_39 VDD33_6 GND_40 VDD33_7 GND_41 VDD33_8 GND_42 VDD33_9 GND_43 VDD33_10 GND_44 VDD33_11 GND_45 VDD33_12 GND_46 VDD33_13 GND_47 GND_48 LRX_AVDD33_1 GND_49 LRX_AVDD33_2 GND_50 GND_51 LTX_AVDD33_1 GND_52 LTX_AVDD33_2 GND_53 LTX_AVDD33_3 GND_54 LTX_AVDD33_4 GND_55 LTX_AVDD33_5 LRX_AVSS33_1 LRX_AVSS33_2 DDR_VREF0 DDR_VREF1 LTX_AVSS33_1 DDR_VREF2 LTX_AVSS33_2 LTX_AVSS33_3 DDR_VDDQ_1 LTX_AVSS33_4 DDR_VDDQ_2 LTX_AVSS33_5 DDR_VDDQ_3 DDR_VDDQ_4 DDR_VDDQ_5 DDRPLL_AVSS33 DDR_VDDQ_6 SYSPLL_AVSS33 DDR_VDDQ_7 ADPLL_AVSS33 DDR_VDDQ_8 SSPLL_AVSS33 DDR_VDDQ_9 DDR_VDDQ_10 DDRPLL_AVDD33 DDR_VDDQ_11 SYSPLL_AVDD33 DDR_VDDQ_12 SSPLL_AVDD33 DDR_VDDQ_13 ADPLL_AVDD33 DDR_VDDQ_14 DDR_VDDQ_15 DDR_VDDQ_16 DDR_VDDQ_17 A2 F5 F7 F8 F9 F10 F11 F12 F14 G5 G14 G16 H7 H8 H9 H10 H11 H12 H14 H15 H16 J7 J8 J9 J10 J11 J12 J14 J15 J16 K7 K8 K9 K10 K11 K12 K14 K15 K16 L14 L15 M7 M8 M9 M10 M11 M12 M14 M15 N5 N6 N15 P5 P11 R4 R14 M16 P16 F4 H4 K4 M4 P4 C17 D17 E16 F16 C18 D18 E17 E18 +3.3V_3D +3.3V_PLL L707 BLM18PG121SN1D C834 0.1uF C773 0.1uF C766 0.1uF C759 0.1uF C839 10uF RF Emiiter Interface P704 12507WS-12L +3.3V +3.3V 1 2 3 4 5 6 7 8 9 10 11 12 13 READY READY READY R1454 R1481 R1482 2.7K 2.7K 2.7K ZD701 5.6B ZD702 5.6B ZD707 5.6B ZD708 5.6B R1456 100 R1483 100 R1484 100 R1477 1K 3D_RF_RXD 3D_RF_TXD 3D_RFMODULE_RESET 3D_RFMODULE_DC 3D_RFMODULE_DD ZD703 5.6B ZD704 5.6B ZD705 5.6B ZD706 5.6B R1453 100 R1469 100 R1470 100 R1455 22 R1478 1K R1479 1K R1480 1K 3D_RF_GPIO0 3D_RF_GPIO1 3D_RF_GPIO2 3D_L/R_SYNC C_DDR_DQ[15] R13 C_DDR_DQ[14] R12 C_DDR_DQ[13] V13 C_DDR_DQ[12] T11 C_DDR_DQ[11] U11 C_DDR_DQ[10] U13 C_DDR_DQ[9] C_DDR_DQ[8] C_DDR_DQ[7] C_DDR_DQ[6] C_DDR_DQ[5] C_DDR_DQ[4] C_DDR_DQ[3] C_DDR_DQ[2] C_DDR_DQ[1] C_DDR_DQM0 C_DDR_DQM1 C_DDR_DQS0M C_DDR_DQS1M C_DDR_DQS0P C_DDR_DQS1P /C_DDR_CS C_DDR2_ODT /C_DDR_RAS /C_DDR_CAS /C_DDR_WE C_DDR2_CLK /C_DDR2_CLK C_DDR2_CKE C_DDR_BA[0] C_DDR_BA[1] C_DDR_DQ[15-0] C_DDR_A[12-0] R758 10K TP7 Serial Flash 2MBit +3.3V_3D SPI_CSZ SPI_DO FLASH_WP C B Q703 KRC103S READY E IC702 W25X20BVSNIG CS 1 DO 2 WP 3 GND 4 VCC 8 HOLD 7 CLK 6 DIO 5 C735 0.1uF 16V SPI_CK SPI_DI LG8300_RESET +3.3V_3D SW700 JTP-1127WEM 1 2 R757 0 3 4 R772 10K C737 0.1uF 16V LG8300_RESET +3.3V_3D EJTAG /JTAG_TRST JTAG_TDI JTAG_TDO JTAG_TMS JTAG_TCLK READY R761 3.3K R763 3.3K R765 3.3K R764 3.3K R768 3.3K 0 R759 R770 1K R776 3.3K TP1 TP2 TP3 TP4 TP5 TP6 +1.8V +1.8V R998 4.7K 1% DDR_VREF_LG8300 R999 4.7K 1% C843 C842 0.1uF 1000pF R996 4.7K 1% R997 4.7K 1% C840 C841 0.1uF 1000pF DDR_VREF_DDR Close to LG8300 Close to DDR2(IC701) THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION. FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC. Copyright © 2011 LG Electronics Inc. All rights reserved. Only for training and service purposes GP2R_S7R 3DF 2010-08-31 7 LGE Internal Use Only