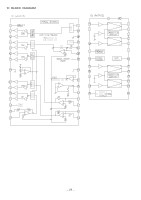

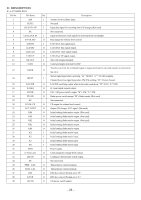

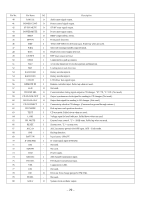

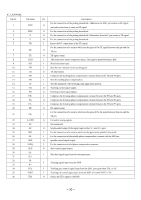

AIWA CDC-X227 Service Manual - Page 32

IC, LC78622NE - mute

|

View all AIWA CDC-X227 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 32 highlights

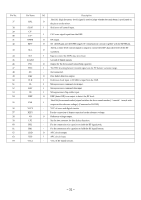

IC, LC78622NE Pin No. Pin Name 1 DEFI 2 TAI 3 PDO 4 VVSS 5 ISET 6 VVDD 7 FR 8 VSS 9 EFMO 10 EFMIN 11 TEST2 12,13 CLV+,CLV- 14 V/P 15 HFL 16 TES 17 TOFF 18 TGL 19 JP+ 20 JP- 21 PCK 22 FSEQ 23 24 ~ 28 29 30 31 32 33 VDD CONT1 ~ 5 EMPH C2F DOUT TEST3 TEST4 34 PCCL 35 LMUTE 36 LVDD 37 LOUT 38 LVSS 39 RVSS 40 ROUT 41 RVDD I/O Description I Defect detection signal (DEF) input. (Must be connected to 0V when not in used.) I For PLL/Test input. A pull-down resistor is built-in. (Must be connected to 0V.) O External VCO control phase comparator output. - Internal VCO ground. (Must be connected to 0V.) I PDO output current adjustment resistor connection. - Internal VCO power supply. I VCO frequency range adjustment. - Digital system ground. (Must be connected to 0V.) O Slice level control EFM signal output. I Slice level control EFM signal input. I Test input. A pull-down resistor is built-in. (Must be connected to 0V.) O Disc motor control output. Can be set to three-value output by microprocessor command. Rough servo/phase control automatic switching monitor output. Output a high level during O rough servo a low level. I Track detection signal input. This is a Schmitt input. I Tracking error signal input. This is a Schmitt input. O Tracking off output. O Tracking gain switching output. Increase the gain when low. Track jump output. Three value output is also possible when specified by microprocessor O command. O EFM data playback clock monitor. Output 4.3218 MHz when the phase is locked. (Not used) Synchronization signal detection output. Output a high level when the synchronization signal O detected from the EFM signal and the internaly generated synchronization signal range.(Not used) - Digital system power supply. I/O General purpose input/ output pin 1 ~ 5. (Not used) O De-emphasis monitor. A high level indicates playback of a De-emphasis disc. (Not used) O C2 flag output. (Not used) O Digital output. (Not used) I Test input. A pull-down resistor is built-in. (Must be connected to 0V.) I Test input. A pull-down resistor is built-in. (Must be connected to 0V.) General purpose input/output command identifying. A pull-down resistor is built-in. I "H": Control possible only for the general purpose input/ output port command. "L": Control possible for all commands. (Must be connected to 0V.) O Left channel mute output. (Not used) - Left channel power supply. O Left channel output. - Left channel ground. (Must be connected to 0V.) - Right channel ground. (Must be connected to 0V.) O Right channel output. - Right channel power supply. - 32 -