Asus TS500-E5 PA4 User Guide - Page 30

Memory mirroring and sparing technology

|

View all Asus TS500-E5 PA4 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 30 highlights

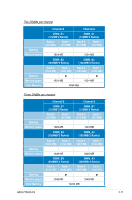

2.3.3 Memory mirroring and sparing technology The Intel® 5100MCH chipset supports the memory sparing technology. Refer to the below section: Memory Sparing At configuration time, a DIMM rank is set aside to replace a defective DIMM rank. When the error rate for a failing DIMM rank reaches a pre-determined threshold, the memory sparing function will issue an interrupt and initiate a spare copy. At the completion of the copy, the failing DIMM rank is disabled and the "spared" DIMM rank will be used in its place. Refer to section 5.4.3 Chipset and configure the options of Channel Rank Sparing or Channel 1 Rank Sparing to enable the memory sparing functions. The default BIOS setting is disabled. • Each channel contains its own sparing engine and can be enabled or disabled separately. • This motherboard does not support rank sparing across channels. • The DIMM rank with the largest size will be assigned as spare rank. Data can only be copied from a smaller sized rank to a larger sized one. • A DIMM can contain only one or two ranks. To support sparing function, a DIMM channel should contain at least two ranks. • When sparing function is enabled, the usable memory size will reduce the size of the spare ranks. The following tables show memory configurations with Memory Sparing function in Channel A/B. One DIMM per channel (two ranks) Sparing Memory space Total Memory Channel B DIMM_B1 (1024MB*2 Ranks) Rank 0 Rank 1 (1024 MB) (1024 MB) Channel A DIMM_A1 (1024MB*2 Ranks) Rank 0 Rank 1 (1024 MB) (1024 MB) 1024 MB 1024 MB 2048 MB 2-10 Chapter 2: Hardware setup