Foxconn Cinema Deluxe English Manual. - Page 51

► Data Cache BG Scrub

|

View all Foxconn Cinema Deluxe manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 51 highlights

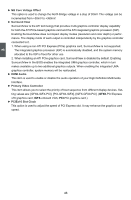

commands may be issued in clocks N+1 through N+9. To program this field, BIOS must convert the tFAW parameter into MEMCLK cycles by dividing the highest tFAW (in ns) across all DIMMs connected to the channel by the lowest period (highest frequency) of MEMCLK (in ns) over all P-states and rounding up to the next integer. ECC Configuration CMOS Setup Utility - Copyright (C) 1985-2009, American Megatrends, Inc. ECC Configuration ECC Configuration Help Item ECC Mode [Disabled] Set the level of ECC DRAM ECC [Disabled] protection. Note:The DRAM SCRUB REDIRECT [Disabled] 'Super' ECC mode 4-Bit ECC Mode [Disabled] dynamically sets the DRAM BG Scrub [Disabled] DRAM scrub rate so Data Cache BG Scrub [Disabled] all of memory is L2 Cache BG Scrub [Disabled] scrubbed in 8 hours. L3 Cache BG Scrub [Disabled] 3 Move Enter:Select +/-/:Value F10:Save ESC:Exit F1:General Help F2/F3:Change Colors F9:Optimized Defaults ► ECC Mode This item is used to set the level of the ECC (Error Checking and Correcting) protection. If you select the 'Super' mode, you can dynamically sets the DRAM scrub rate so all of the memory is scrubbed in 8 hours. When you select the 'User', you can enabled or disable the following items. ► DRAM ECC It allows hardware to report and correct memory errors automatically maintaining system integrity. ► DRAM SCRUB REDIRECT It allows the system to correct DRAM ECC errors immediately, when they occur, even if background scrubbing is on. ► 4-Bit ECC Mode It is used to enable or disable 4-BIT ECC Mode.(Note: Also known as CHIPKILL ECC Mode) ► DRAM BG Scrub This item is used to correct memory errors so later reads are correct. Doing this while memory is not being used improves performance.(Note: When AMD's node interleave feature is enabled, BIOS will force DRAM scrub off.) ► Data Cache BG Scrub It allows the L1 Data Cache ram to be corrected while idle. ► L2 Cache BG Scrub It allows the L2 Data Cache ram to be corrected while idle. ► L3 Cache BG Scrub It allows the L3 Data Cache ram to be corrected while idle. 44