HP Brio ba300 hp brio ba300, technical reference manual (product description) - Page 29

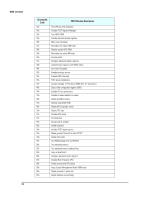

Order in Which POST Tests are Performed

|

View all HP Brio ba300 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 29 highlights

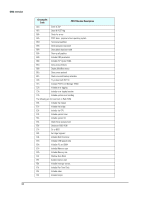

BIOS overview Order in Which POST Tests are Performed Each time the system is powered on, or a reset is performed, the POST is executed. The POST process verifies the basic functionality of the system components and initializes certain system parameters. The POST starts by displaying a graphic screen of the Hewlett-Packard logo when the PC is restarted. Devices, such as memory and newly installed hard disks, are configured automatically. The user is not requested to confirm the change. Newly removed hard disks are detected, and the user is prompted to confirm the new configuration by pressing . Note, though, that the POST does not detect when a hard disk drive has been otherwise changed. During the POST, the BIOS and other ROM data is copied into high-speed shadow RAM. The shadow RAM is addressed at the same physical location as the original ROM in a manner which is completely transparent to applications. It therefore appears to behave as very fast ROM. This technique provides faster access to the system BIOS firmware. The following table lists the POST checkpoint codes written at the start of each test. Checkpoint Code 02h 03h 04h 06h 08h 09h 0Ah 0Bh 0Ch 0Eh 0Fh 10h 11h 12h 13h 14h 17h 18h 1Ah 1Ch 24h 26h 28h 29h 2Ah POST Routine Description Verify Real Mode Disable Non-Maskable Interrupt (NMI) Get CPU type Initialize system hardware Initialize chipset with initial POST values Set IN POST flag Initialize CPU registers Enable CPU cache Initialize caches to initial POST values Initialize I/O component Initialize the local bus IDE Initialize Power Management Load alternate registers with initial POST values Restore CPU control word during warm boot Initialize PCI Bus Mastering devices Initialize keyboard controller Initialize cache before memory autosize 8254 timer initialization 8237 DMA controller initialization Reset Programmable Interrupt Controller Set ES segment register to 4 GB Enable A20 line Autosize DRAM Initialize POST Memory Manager Clear 512 KB base RAM 29