HP Brio ba300 hp brio ba300, technical reference manual (product description) - Page 30

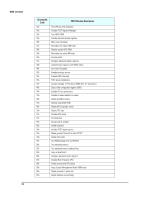

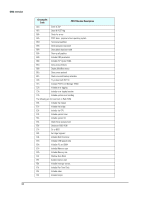

BIOS overview, Checkpoint, POST Routine Description

|

View all HP Brio ba300 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 30 highlights

BIOS overview 30 Checkpoint Code 32h 33h 34h 35h 36h 37h 38h 39h 3Ah 3Ch 3Dh 40h 42h 44h 45h 47h 48h 49h 4Ah 4Bh 4Ch 4Eh 50h 51h 52h 54h 56h 59h 5Ah 5Bh 5Ch 60h 62h 64h 66h 67h 68h 69h 6Ah 6Ch POST Routine Description Test CPU bus-clock frequency Initialize POST Dispatch Manager Test CMOS RAM Initialize alternate chipset registers Warm start shutdown Reinitialize the chipset (MB only) Shadow system BIOS ROM Reinitialize the cache (MB only) Autosize cache Configure advanced chipset registers Load alternate registers with CMOS values Set initial CPU speed Initialize interrupt vectors Initialize BIOS interrupts POST device initialization Initialize manager for PCI Option ROMs (Rel. 5.1 and earlier) Check video configuration against CMOS Initialize PCI bus and devices Initialize all video adapters in system Display QuietBoot screen Shadow video BIOS ROM Display BIOS copyright notice Display CPU type Initialize EISA board Test keyboard Set key click if enabled Enable keyboard Initialize POST display service Display prompt "Press F2 to enter SETUP" Disable CPU cache Test RAM between 512 and 640 KB Test extended memory Test extended memory address lines Jump to UserPatch1 Configure advanced cache registers Initialize Multi Processor APIC Enable external and CPU caches Setup System Management Mode (SMM) area Display external L2 cache size Display shadow-area message