Intel D2550DC2 Technical product specification - Page 71

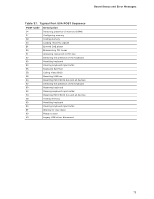

Port 80h POST Codes, Table 35., Port 80h POST Code Ranges

|

View all Intel D2550DC2 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 71 highlights

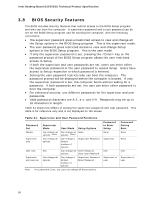

Board Status and Error Messages 4.4 Port 80h POST Codes During the POST, the BIOS generates diagnostic progress codes (POST codes) to I/O port 80h. If the POST fails, execution stops and the last POST code generated is left at port 80h. This code is useful for determining the point where an error occurred. Displaying the POST codes requires a PCI bus add-in card, often called a POST card. The POST card can decode the port and display the contents on a medium such as a seven-segment display. NOTE The POST card must be installed in the PCI bus connector. The following tables provide information about the POST codes generated by the BIOS: • Table 35 lists the Port 80h POST code ranges • Table 36 lists the Port 80h POST codes themselves • Table 37 lists the Port 80h POST sequence NOTE In the tables listed above, all POST codes and range values are listed in hexadecimal. Table 35. Port 80h POST Code Ranges Range 0x00 - 0x05 0x10, 0x20, 0x30 0x11 - 0x1F 0x21 - 0x29 0x2A - 0x2F 0x31 - 0x35 0x36 - 0x3F 0x41 - 0x4F 0x50 - 0x5F 0x60 - 0x6F 0x70 - 0x7F 0x80 - 0x8F 0x90 - 0x9F 0xA0 - 0xAF 0xB0 - 0xBF 0xC0 - 0xCF 0xD0 - 0xDF Subsystem Entering SX states S0 to S5. Resuming from SX states (0x10 - 0x20 - S2, 0x30 - S3, etc.) PEI phase pre MRC execution MRC memory detection PEI phase post MRC execution Recovery Platform DXE driver CPU Initialization (PEI, DXE, SMM) I/O Buses: PCI, USB, ATA etc. 0x5F is an unrecoverable error. Start with PCI. BDS Output devices: All output consoles. For future use Input devices: Keyboard/Mouse. For future use Boot Devices: Includes fixed media and removable media. Not that critical since consoles should be up at this point. For future use For future use 71