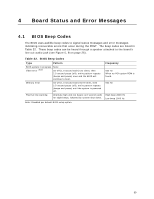

Intel D2550DC2 Technical product specification - Page 72

Table 36., Port 80h POST Codes, Intel Desktop Board D2550DC2 Technical Product Specification

|

View all Intel D2550DC2 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 72 highlights

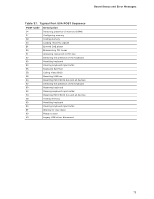

Intel Desktop Board D2550DC2 Technical Product Specification Table 36. Port 80h POST Codes Port 80 Code Progress Code Enumeration ACPI S States 0x00,0x01,0x02,0x03,0x04,0x05 Entering S0, S2, S3, S4, or S5 state 0x10,0x20,0x30 Resuming from S2, S3, S4, or S5 state 0x11 0x12 0x13 0x14 0x15 0x16 0x17 0x18 0x21 0x24 0x25 0x27 0x28 0x31 0x33 0x34 0x41 0x42 0x43 0x44 0x45 0x46 PEI before MRC PEI Platform driver Set boot mode, GPIO init Early chipset register programming Basic chipset initialization LAN init Exit early platform init driver PEI SMBUS SMBUS driver init Entry to SMBUS execute read/write Exit SMBUS execute read/write Memory MRC entry point Detecting presence of memory DIMMs Override Detected DIMM settings Configuring memory. Testing memory PEIMs/Recovery Crisis Recovery has initiated Loading recovery capsule Start recovery capsule / valid capsule is found CPU Initialization CPU PEI Phase Begin CPU PEI Init XMM instruction enabling End CPU PEI Init CPU PEI SMM Phase Begin CPU SMM Init smm relocate bases Smm relocate bases for APs End CPU SMM Init continued 72