Intel DP55WB Product Specification - Page 80

Table 40., Lead-Free Board Markings

|

UPC - 735858209151

View all Intel DP55WB manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 80 highlights

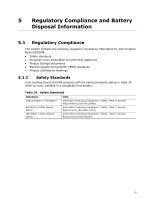

Intel Desktop Board DP55WB Technical Product Specification Table 40. Lead-Free Board Markings Description Lead-Free 2nd Level Interconnect: This symbol is used to identify electrical and electronic assemblies and components in which the lead (Pb) concentration level in the desktop board substrate and the solder connections from the board to the components (second-level interconnect) is not greater than 0.1% by weight (1000 ppm). Mark or or 80

Intel Desktop Board DP55WB Technical Product Specification

80

Table 40.

Lead-Free Board Markings

Description

Mark

Lead-Free 2

nd

Level Interconnect:

This symbol is used to identify

electrical and electronic

assemblies and components in

which the lead (Pb) concentration

level in the desktop board

substrate and the solder

connections from the board to the

components (second-level

interconnect) is not greater than

0.1% by weight (1000 ppm).

or

or