Intel DQ57TM Product Specification - Page 58

Clear CMOS Header

|

View all Intel DQ57TM manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 58 highlights

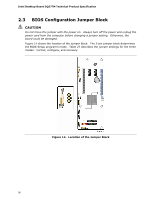

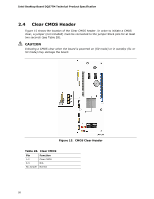

Intel Desktop Board DQ57TM Technical Product Specification 2.4 Clear CMOS Header Figure 15 shows the location of the Clear CMOS header. In order to initiate a CMOS clear, a jumper (not included) must be connected to the jumper block pins for at least two seconds (see Table 28). CAUTION Initiating a CMOS clear when the board is powered on (S0 mode) or in standby (S1 or S3 mode) may damage the board. Figure 15. CMOS Clear Header Table 28. Clear CMOS Pin Function 1-2 Clear CMOS 2-3 N/A No Jumper Normal 58

Intel Desktop Board DQ57TM Technical Product Specification

58

2.4

Clear CMOS Header

Figure 15 shows the location of the

Clear CMOS header. In order to initiate a CMOS

clear, a jumper (not included) must be connected to the jumper block pins for at least

two seconds (see Table 28).

CAUTION

Initiating a CMOS clear when the board is powered on (S0 mode) or in standby (S1 or

S3 mode) may damage the board.

Figure 15.

CMOS Clear Header

Table 28.

Clear CMOS

Pin

Function

1-2

Clear CMOS

2-3

N/A

No Jumper

Normal