LG KU250 Service Manual - Page 49

External memory interface - specs

|

View all LG KU250 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 49 highlights

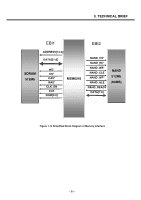

3. TECHNICAL BRIEF 3.10 External memory interface The MSM6245 device was designed to provide two distinct memory interfaces. EBI1 was targeted for supporting high speed synchronous memory devices. EBI2 was targeted towards supporting slower asynchronous devices such as LCD, NAND flash, SDRAM, etc. • EBI1 Features - 16 bit static and dynamic memory interface - 32 bit dynamic memory interface - 24 bits of address for static memory devices which can support up to 32MBytes on each chip select - Synchronous burst memories supported (burst NOR, burst PSRAM) - Synchronous DRAM memories supported - Byte addressable memory supporting 8 bit, 16 bit and 32 bit accesses - Pseudo SRAM (PSRAM) memory support • EBI2 Features - Support for asynchronous FLASH and SRAM(16bit & 8bit). - Interface support for byte addressable 16bit devices (UB_N & LB_N signals). - Support for 8 bit/16bit wide NAND flash. - Support for parallel LCD interfaces, port mapped of memory mapped(18 or 16 bit). • 512Mb NAND(8bit) flash memory + 512Mb SDRAM (32bit) Device FLASH SDRAM Part Name HYC0UEH0MF3P HYC0UEH0MF3P Interface Spec Maker hynix hynix Read Access Time 60 ns 7 ns Write Access Time 60 ns 7 ns Table#1. External memory interface - 50 -