Sony STR-DB830 Service Manual - Page 27

Ic Pin Function Description - reset

|

View all Sony STR-DB830 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 27 highlights

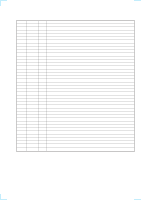

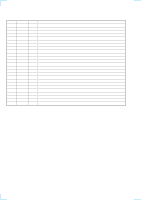

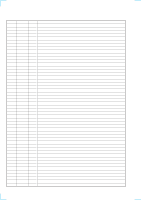

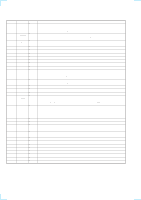

4-22. IC PIN FUNCTION DESCRIPTION IC1401 CXD2712R AUDIO DSP(DIGITAL BOARD) Pin No. Pin Name I/O 1 VSS3 - 2 - 5 SOA - SOD O 6, 7 ECJ0, ECJ1 I 8 - NC 9 XHDWR I 10 XHDRD I 11 VSS4 - 12 VDD2 - 13 HRDY O 14 XHDCS I 15 HA0 I 16 - 20 HD0 - HD4 I/O 21 VSS5 - 22 VDD3 - 23 - 25 HD5 - HD7 I/O 26 XRST I 27 - 30 FGP0 - FGP3 O 31 VSS6 - 32 - 40 ED0 - ED8 I/O 41 VSS7 - 42 VDD4 - 43 - 49 ED9 - ED15 I/O 50 TSTD I 51 VSS8 - 52 VDD5 - 53 - 60 ED16 - ED23 I/O 61 VSS9 - 62 - 69 ED24 - ED31 I/O 70 XOE O 71 VSS10 - 72 VDD6 - 73 CAS O 74 XWE O 75 RAS O 76 - 80 EA0 - EA4 I/O 81 VSS11 - 82 VDD7 - 83 -89 EA5 - EA11 I/O 90 EA12 O Description Ground Serial data output Conditional jump input terminal (7pin Connected to ground) No connection HCIF data write HCIF data read Ground +3.3V HCIF ready signal Open drain HCIF chip select HCIF address input HCIF data input/output Ground +3.3V HCIF data input/output Reset input "L": active Test data output Ground External RAM data input/output Ground +3.3V External RAM data input/output Test data input "L" = normal "H" = test (Connected to ground) Ground +3.3V External RAM data input/output Ground External RAM data input/output External RAM output enable Ground +3.3V External RAM column address strobe (Not used) External RAM write enable (Not used) External RAM raw address strobe External RAM address output/test data input Ground +3.3V External RAM address output/test data input External RAM address output - 49 -