Sony STR-DB830 Service Manual - Page 33

Sony STR-DB830 - Fm Stereo/fm-am Receiver Manual

|

View all Sony STR-DB830 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 33 highlights

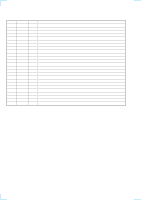

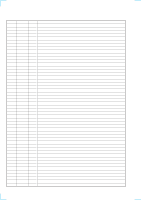

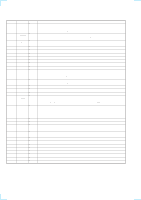

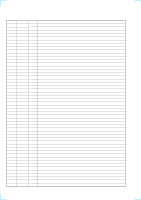

Pin No. 31 32 33 34 Pin Name RIN- RIN+ VREFL VCOM 35 VREFH 36 A. 5V 37 A. GND 38 XTI 39 MCLKI 40 S/P 41 CS 42 CCLK 43 CDTI 44 CDTO I/O Description I Rch analog negative input pin I Rch analog positive input pin I Negative voltage reference input pin, AVSS (Connected to ground) Common voltage output pin, AVDD/2 O Large external capacitor is used to reduce power-supply noise I Positive voltage reference input pin, AVDD - Analog power supply pin - Analog ground pin I X'tal input pin (Not used) I External master clock input pin if XTS = "L" Parallel/serial select pin I "L": serial control mode, "H": parallel control mode (Connected to ground) I Chip select pin in serial mode I Control data clock pin in serial mode I Control data input in serial mode O Control data output pin in serial mode If pins TEST, ICKS0, ICKS1, PD, S/P, DFS, DEM0, DEM1, CAD0, CAD1, S/M, MCLK, SDOS are not driven, then TEST, ICKS0, ICKS1, CAD0, CAD1, must be tied to either AVSS or AVDD. PD, S/P, DFS, DEM0, DEM1, S/M, MCLK, SDOS must be tied to either DVSS or DVDD. - 55 -