Sony STR-DB830 Service Manual - Page 37

Ic Block Diagrams

|

View all Sony STR-DB830 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 37 highlights

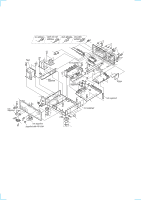

4-23. IC BLOCK DIAGRAMS IC1206 NJM2103M (DIGITAL BOARD) CR 1 VSC 2 +- OUTC 3 GND 4 VREF Q RS 8 RESET -+ 7 VSA 6 VSB/SESIN 5 V+ +- +- XO XI VDD2 VSS2 T1 T2 IC1 BU1924F (TUNER BOARD) 16 15 RCLK NC 14 13 12 11 10 9 DIGITAL PLL 1187.5Hz PLL 57kHz RDS/ARI COMPARATOR CLOCK ANALOG BIPHASE DECODER DEFFERENTIAL DECODER 8th SWITCHED CAPACITOR FILTER ANTI-ALIASING FILTER 1 2 3 4 56 7 8 TEST QUAL RDAT VREF MUX VDD1 VSS1 VSS3 CMP - 59 -

— 59 —

4-23.

IC BLOCK DIAGRAMS

IC1206 NJM2103M (DIGITAL BOARD)

1

2

3

4

5

6

7

8

V+

VSB/SESIN

VSA

RESET

GND

OUTC

VSC

CR

VREF

+

–

–

+

–

+

–

+

Q

R

S

IC1 BU1924F (TUNER BOARD)

ANALOG

DIGITAL

RCLK

NC

XO

XI

VSS2

T2

VDD2

T1

QUAL

RDAT

VREF

MUX

VDD1

VSS1

VSS3

CMP

1

4

3

6

5

8

7

2

14

15

16

13

12

11

10

9

CLOCK

PLL 57kHz

RDS/ARI

COMPARATOR

8th SWITCHED

CAPACITOR

FILTER

ANTI-ALIASING

FILTER

BIPHASE

DECODER

PLL

1187.5Hz

DEFFERENTIAL

DECODER

TEST