Lenovo ThinkPad 600E Technical Reference Manual for the ThinkPad 600 - Page 17

Specifications, Performance Specifications,

|

View all Lenovo ThinkPad 600E manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 17 highlights

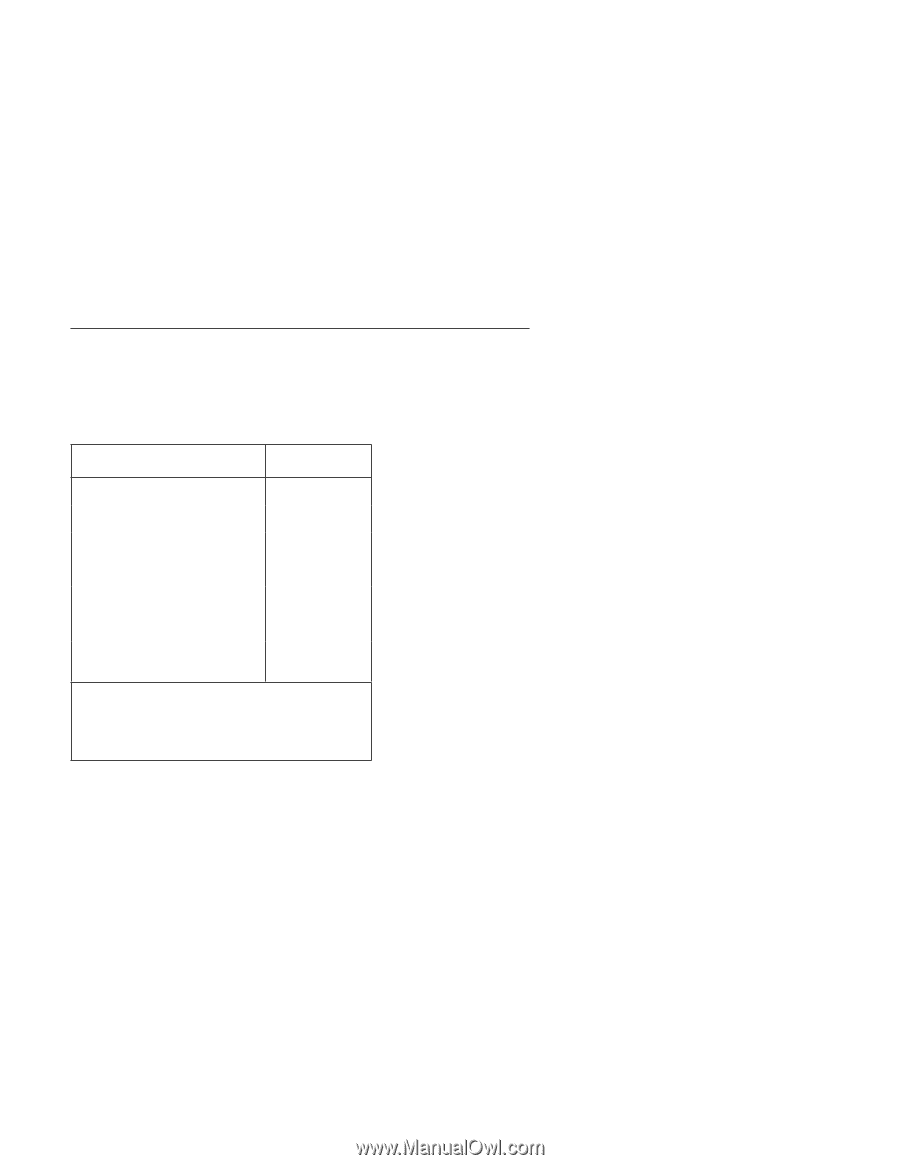

Specifications Figure 1-4 to Figure 1-7 list the specifications for the computers. Performance Specifications Device/Cycle Clock Counts (66 MHz) Microprocessor L1 cache (64bit) read/write hit L2 cache (64bit) (for not all models) read hit (back-to-back) write hit (back-to-back) Memory (64bit) (see Note) read, page hit read, bank miss read, page miss posted write write retire rate from write buffer Note: 233 or 266 MHz 1 CPUCLK 3-1-1-1(1-1-1-1) 5-1-1-1 8-1-1-1 11-1-1-1 3-1-1-1 -1-1-1 The cycle times shown for access to system board RAM are based on 66 MHz memory bus (SDRAM, CAS LATENCY=2) Figure 1-4. Performance Specifications System Overview 1-7

Specifications

Figure

1-4 to Figure

1-7 list the specifications for the computers.

Performance Specifications

Figure

1-4. Performance Specifications

Device/Cycle

Clock Counts

(66 MHz)

Microprocessor

233 or 266

MHz

L1 cache (64bit)

read/write hit

1 CPUCLK

L2 cache (64bit) (for not all

models)

read hit (back-to-back)

write hit (back-to-back)

3-1-1-1(1-1-1-1)

Memory (64bit) (see Note)

read, page hit

read, bank miss

read, page miss

5-1-1-1

8-1-1-1

11-1-1-1

posted write

write retire rate from

write buffer

3-1-1-1

-1-1-1

Note:

The cycle times shown for access to system

board RAM are based on 66 MHz memory bus

(SDRAM, CAS LATENCY=2)

System Overview

1-7