Asus K8N-DL User Guide - Page 85

L2 Cache Background Scrubber [Disabled]

|

View all Asus K8N-DL manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 85 highlights

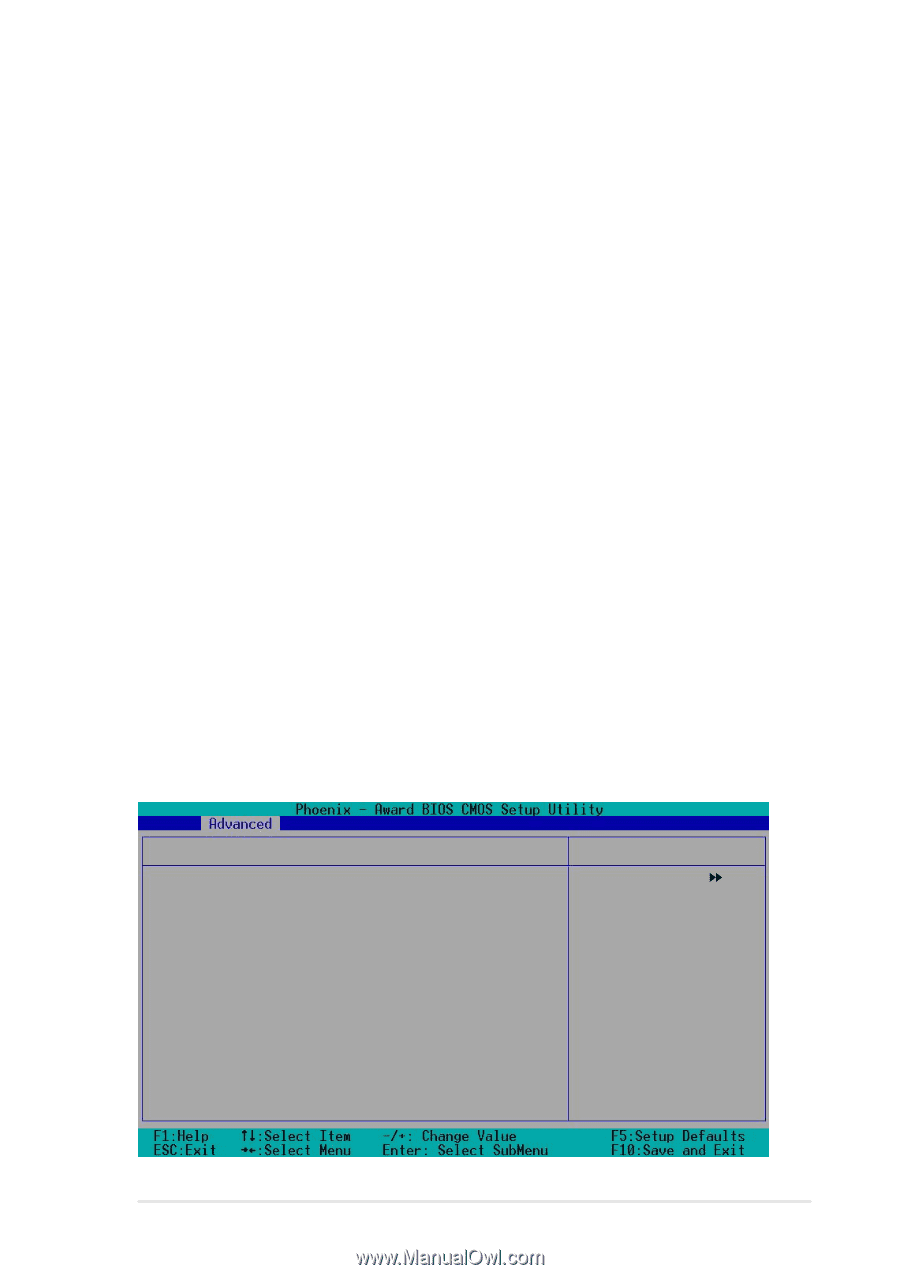

Chip-Kill Mode Enable [Disabled] When set to [Enabled], allows ECC checking to be based on a 128/16 data/ECC rather than on a 64/8 data/ECC. You may only enable this feature in 128-bit DRAM data width mode. Configuration options: [Disabled] [Enabled] ECC Redirection [Disabled] When set to [Enabled], correctable errors are corrected as the data is passed to the requestor. The data in the DRAM is not corrected if this item is set to [Disabled]. Configuration options: [Disabled] [Enabled] DRAM Background Scrubber [Disabled] Specifies the scrub rate of the next address to be scrubbed by the DRAM scrubber. Configuration options: [Disabled] [40.0ns] L2 Cache Background Scrubber [Disabled] Specifies the scrub rate of the next address to be scrubbed by the L2 cache scrubber. Configuration options: [Disabled] [40.0ns] DCache Background Scrubber [Disabled] Specifies the scrub rate of the next address to be scrubbed by the data cache scrubber. Configuration options: [Disabled] [40.0ns] 4.4.3 Chipset This menu shows the chipset configuration settings. Select an item then press to display a pop-up menu with the configuration options. Chipset OnChip IDE Channel0 OnChip IDE Channel1 Hyper Transport Frequency Hyper Transport Width Errata 94 Enhanced System BIOS Cacheable Spread Spectrum SATA Spread Spectrum PCIE Spread Spectrum SSE/SSE2 Instructions Init Display First IDE DMA Transfer Access Serial-ATA 1 SATA DMA Transfer Serial-ATA 2 SATA2 DMA Transfer IDE Prefetch Mode [Enabled] [Enabled] [4x] [↓16 ↑16] [Auto] [Disabled] [Enabled] [Disabled] [Disabled] [Enabled] [PCI Slot] [Enabled] [Enabled] [Enabled] [Enabled] [Enabled] [Enabled] Select Menu Item Specific Help Disable/Enable OnChip IDE Channel0. ASUS K8N-DL 4-23