HP DL360 The Intel processor roadmap for industry-standard servers technology

HP DL360 - ProLiant - G3 Manual

|

UPC - 613326948835

View all HP DL360 manuals

Add to My Manuals

Save this manual to your list of manuals |

HP DL360 manual content summary:

- HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 1

industrystandard servers technology Extended hyper-pipeline...10 SSE3 instructions...10 64-bit extensions -Intel Microarchitecture Nehalem ...15 Integrated memory controller...15 Intel® QuickPath Dynamic Power Management...19 Performance comparisons...20 TPC-C performance ...20 SPEC performance - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 2

they affect HP industry-standard enterprise servers. Introduction As standards-based computing has pushed into the enterprise server market, -standard enterprise server market. Intel processor architecture and microarchitectures The Intel processor architecture refers to its x86 instruction set and - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 3

features such as number of cores, architecture, cache, power dissipation, and embedded Intel technologies. Table 1. Intel processor processor 7000 sequence Platform Uni-processor servers Two-processor high-volume servers and workstations Enterprise servers with 4 to 32 processors Intel enhances - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 4

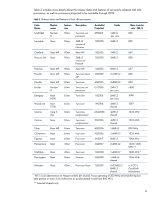

Table 2. Release dates and features of Intel x86 processors Code Name Market name Feature size Description Available/ Projected Cache Max. transfer rate * (MT/s) Smithfield Pentium 90nm Two-core uni- 2H2005 1MB L2 800 D processor per core Irwindale Xeon 90nm 2MB L2 1Q2005 2MB - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 5

to the Pentium 4 and Xeon processors and later added support for 800 MHz to the Pentium 4. • Integer arithmetic logic unit (ALU) running at twice the clock speed (double data rate) • Modified floating point unit (FPU) • Streaming SIMD extension 2 (SSE2): New instructions bring the total to 144 SIMD - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 6

" of the microprocessor; the execution engine; and the retire unit (Figure 4). The front end fetches the instruction and decodes it into smaller instructions (commonly referred to as micro-ops). These decoded instructions are sent to one of the three types of execution units (integer, load/store, or - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 7

aided by a large branch target array that stored branch predictions. Hyper-Threading Technology Intel Hyper-Threading (HT) Technology is a design enhancement for server environments. It takes advantage of the fact that, according to Intel estimates, the utilization rate for the execution units in - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 8

these operating systems can send two instruction 1b, but does not need to wait for 1a. Similarly, if two arithmetic units are available, 4a and 4b can execute at the same time. According to Intel's simulations, HT Technology achieves its objective of improving the microarchitecture utilization rate - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 9

2000 Server does not make this distinction between physical and logical processors and fills the licensing limit based on the number of processors the BIOS discovers at boot. According to Intel, the system requirements for HT Technology are as follows: • A processor that supports HT Technology2 - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 10

. HP expects that any minor differences will be handled by the OS and compiler, so that the average application writer or customer should see no differences. New operating systems are required to make use of 64-bit extensions. Red Hat, SUSE, and Microsoft provide AMD64 support and Intel 64 support - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 11

its volume, can carry more water than a smaller pipe with a higher flow rate. Likewise, the two-core architecture is designed to make processors perform more efficiently at lower frequencies (and lower power consumption levels). The two-core processor allows a better balance between performance and - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 12

. Xeon 3000 Sequence processors use the Intel 3000 or 3010 chipsets which support Error Correction Code (ECC) memory for a high level of data integrity, reliability, and system uptime. ECC can detect multiple-bit memory errors and locate and correct single-bit errors to keep business applications - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 13

3.0 GHz, with 2 MB of L2 cache per core. This configuration delivers a significant increase in processing capacity utilizing the Intel 5000 series chipsets. ProLiant 300 series servers use the Intel 5000P and 5000Z chipsets. These chipsets support 1066-MHz and 1333-MHz Two Independent Buses, DDR2 FB - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 14

appropriate ROM firmware or operating system interface, programmers can use the exposed hardware registers to switch a processor between different performance states, or P-states3, at different power consumption levels. For example, HP developed a power management feature called HP Power Regulator - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 15

processor, it can do so through the QuickPath Interconnect (QPI). 4 For more information, refer to the technology brief "Server virtualization technologies for x86-based HP BladeSystem and HP ProLiant servers" at http://h20000.www2.hp.com/bc/docs/support/SupportManual/c01067846/c01067846.pdf 15 - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 16

processors and other system components. It replaces the multi-drop front-side bus and memory controller hub found each direction for a total theoretical bandwidth of 25.6 GB/s. Reliability, Availability, and Serviceability (RAS features) of the QPI include self-healing links and clock fail-over. - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 17

, L1 cache that is split into two 32-kilobyte caches storing data and instructions • An individual, 256-kilobyte, L2 cache for each core for lower latency QPI, 800/1066 MHz DDR3, HyperThreading L5506 (2.13 GHz) 4MB L3, 4.8 GT/s QPI, 800 MHz DDR3, No HyperThreading 80W E5540 (2.53 GHz) E5530 (2. - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 18

processor operates only at the rated frequency. When Turbo Boost is set to Automatic, the OS requests a higher performance state and the processor determines the optimum frequency. When Turbo Boost is set to Manual, the user can manually disable cores using the BIOS (reboot required) and increase - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 19

disabled through the BIOS during POST. Dynamic Power Management Dynamic Power Management works hand-in-hand with Turbo Boost to automatically optimize the performance and power use of the processor, chipset, and memory based on business requirements. Dynamic Power Management provides the following - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 20

that can be used to compare compute-intensive workloads on different computer systems. SPEC results for Woodcrest, Clovertown, Tulsa, Tigerton, and Nehalem processors are compared in Figure 15. SPEC CPU2006 contains two benchmark suites: CINT2006 for measuring and comparing compute-intensive - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 21

compared to Woodcrest Conclusion Intel processors continue to provide dramatic increases in the processing capability of HP industrystandard servers. In addition to improved system performance, multi-core Intel processors offer greater energy efficiency to help HP customers manage power costs. 21 - HP DL360 | The Intel processor roadmap for industry-standard servers technology - Page 22

below. Resource description Web address ProLiant servers home page www.hp.com/servers/proliant Power Regulator for ProLiant Servers ISS Technology Papers http://h20000.www2.hp.com/bc/docs/support/Su pportManual/c00300430/c00300430.pdf www.hp.com/servers/technology Call to action Send comments

The Intel

®

processor roadmap for industry-

standard servers

technology brief, 10

th

Edition

Abstract

..............................................................................................................................................

2

Introduction

.........................................................................................................................................

2

Intel processor architecture and microarchitectures

...................................................................................

2

NetBurst

®

microarchitecture

...................................................................................................................

5

Hyper-pipeline and clock frequency

....................................................................................................

5

Hyper-Threading Technology

..............................................................................................................

7

NetBurst microarchitecture on 90nm silicon process technology

.............................................................

9

Extended hyper-pipeline

...............................................................................................................

10

SSE3 instructions

.........................................................................................................................

10

64-bit extensions —Intel 64

..........................................................................................................

10

Two-core technology

.......................................................................................................................

11

Intel Core™ microarchitecture

..............................................................................................................

12

Processors

......................................................................................................................................

12

Xeon two-core processors

................................................................................................................

12

Xeon four-core processors

................................................................................................................

13

Enhanced SpeedStep® Technology

...............................................................................................

14

Intel Virtualization® Technology

....................................................................................................

15

Intel

®

Microarchitecture Nehalem

.........................................................................................................

15

Integrated memory controller

............................................................................................................

15

Intel

®

QuickPath Technology

............................................................................................................

16

Three-level cache hierarchy

..............................................................................................................

17

Intel

®

Hyper-Threading Technology

...................................................................................................

18

Intel

®

Turbo Boost Technology

..........................................................................................................

18

Dynamic Power Management

...........................................................................................................

19

Performance comparisons

....................................................................................................................

20

TPC-C performance

.........................................................................................................................

20

SPEC performance

..........................................................................................................................

20

Conclusion

........................................................................................................................................

21

For more information

..........................................................................................................................

22

Call to action

.....................................................................................................................................

22