HP DL360 The Intel processor roadmap for industry-standard servers technology - Page 12

Intel Core™ microarchitecture, Processors, Xeon two-core processors

|

UPC - 613326948835

View all HP DL360 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 12 highlights

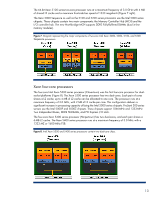

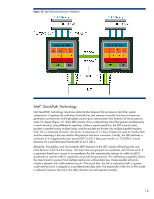

Intel Core™ microarchitecture In 2006, Intel introduced the Core microarchitecture to extend the NetBurst microarchitecture features and to add the energy efficient features of Intel's mobile microarchitecture. The Core microarchitecture uses less power and produces less heat than previous generation Intel processors. The Core microarchitecture features the following technologies that improve per-watt performance and energy efficiency: • Intel® Wide Dynamic Execution enables delivery of more instructions per clock cycle to improve execution time and energy efficiency. • Intel® Intelligent Power Capability reduces power consumption and design requirements. • Intel® Smart Memory Access improves system performance by optimizing the use of the available data bandwidth from the memory subsystem. • Intel® Advanced Smart Cache is optimized for multi-core and two-core processors to reduce latency to frequently used data, providing a higher-performance, more efficient cache subsystem. • Intel® Advanced Digital Media Boost improves performance when executing SSE, SSE2, and SSE3 instructions. This technology accelerates a broad range of encryption, financial, engineering, and scientific applications. • Streaming SIMD Extensions 4 (SSE4) instructions consist of 54 instructions that enhance video, graphics, and high-performance applications. These instructions are divided into two major categories-Vectorizing Compiler and Media Accelerators, and Efficient Accelerated String and Text Processing. Processors The two-core Intel Xeon 3000 and 5000 Sequence and the 7300 series processors are based on the Core microarchitecture. Using Hyper-Threading technology, two-core processors (with the exception of the Xeon 3000 Sequence processors) can simultaneously execute four software threads, thereby increasing processor utilization. To avoid saturation of the Front Side Bus (FSB), the Intel 5000 chipset widens the interface by providing dual independent buses. The Xeon 7300 series processors introduce an independent point-to-point interface between the chipset and each processor that allows full front-side-bus bandwidth. Xeon two-core processors The 64-bit Intel Xeon 3000 Sequence processors combine performance and power efficiency to enable smaller, quieter systems. Xeon 3000 Sequence processors run at a maximum frequency of 2.66 gigahertz (GHz), with 4 megabytes (MB) of shared L2 cache (Figure 7 left) and a maximum front-side bus speed of 1066 megahertz. These processors are compatible with IA-32 software and support single-processor operation. Xeon 3000 Sequence processors use the Intel 3000 or 3010 chipsets which support Error Correction Code (ECC) memory for a high level of data integrity, reliability, and system uptime. ECC can detect multiple-bit memory errors and locate and correct single-bit errors to keep business applications running smoothly. The 64-bit Intel Xeon 5000 Sequence processors have two complete processor cores, including caches, buses, and execution states. The Xeon 5000 Sequence processors run at a maximum frequency of 3.73 GHz, with 2 MB of L2 cache per core. The processor supports maximum front-side bus speeds of 1066 megahertz (Figure 7 center). 12