HP DL360 The Intel processor roadmap for industry-standard servers technology - Page 16

Intel® QuickPath Technology, Intel Microarchitecture Nehalem

|

UPC - 613326948835

View all HP DL360 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 16 highlights

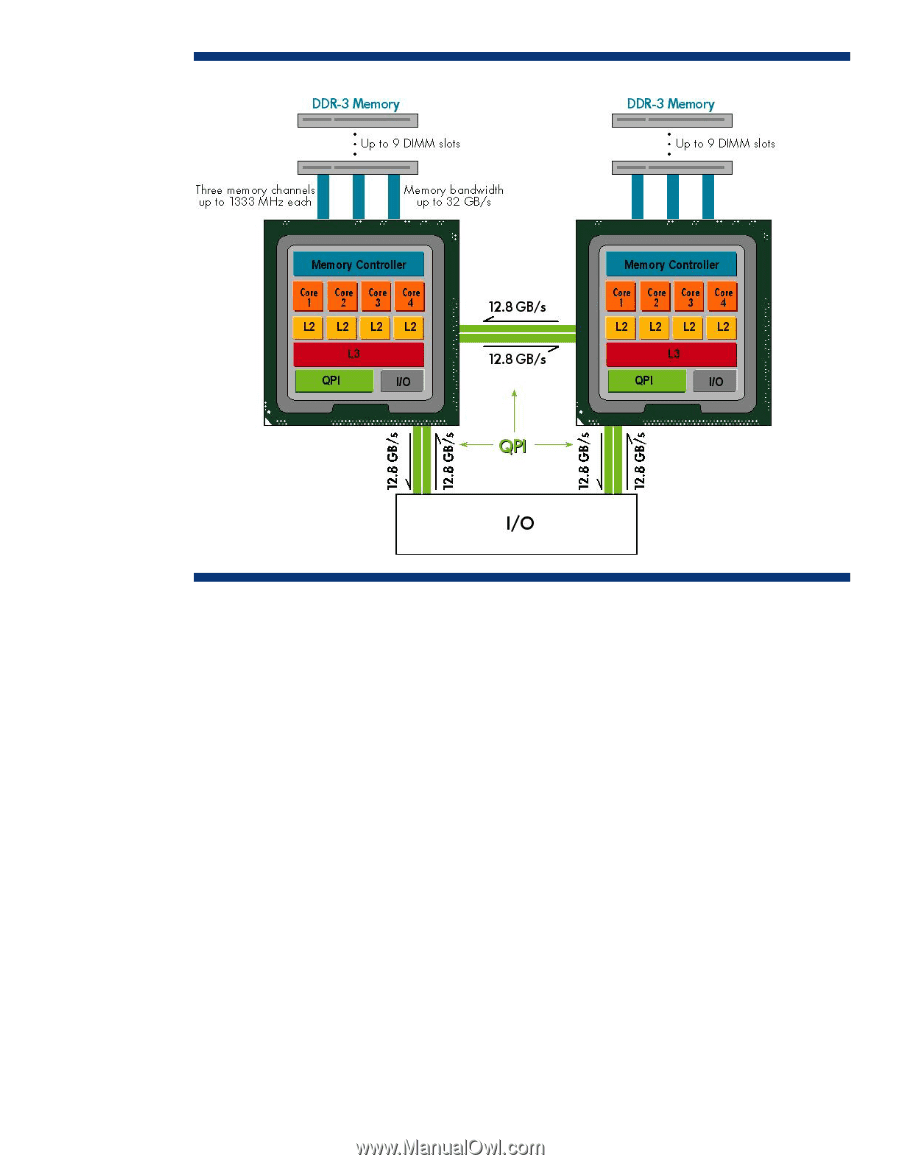

Figure 10. Intel Microarchitecture Nehalem Intel® QuickPath Technology Intel QuickPath Technology maximizes data transfer between the processors and other system components. It replaces the multi-drop front-side bus and memory controller hub found in previous generation architectures with high-speed, point-to-point interconnects that directly link the processors and I/O chipset (Figure 11). Each QPI consists of two unidirectional links that operate simultaneously in each direction using differential signaling. Unlike a typical serial bus, the QPI transmits data packets in parallel across multiple lanes, and the packets are broken into multiple parallel transfers. Each link is comprised of twenty 1-bit lanes. A maximum of 16 bits (2 bytes) are used to transfer data and the remaining 4 bits are used for the protocol and error correction. Initially, the QPI performs a maximum of 6.4 gigatransfers per second (GT/s) with 2 bytes per transfer, or 12.8-GB/s in each direction for a total theoretical bandwidth of 25.6 GB/s. Reliability, Availability, and Serviceability (RAS features) of the QPI include self-healing links and clock fail-over. Each link has twenty 1-bit lanes that are grouped into quadrants with 5 lanes each. If a persistent (hard) error occurs in one quadrant, the link automatically reduces its width to half (2 quadrants) or quarter-width (1 quadrant) using only the good lanes. This self-healing capability allows the interconnect to recover from multiple hard errors without data loss. Unrecoverable soft errors initiate a dynamic link width reduction cycle. If the clock fails, the link is reduced to half- or quarterwidth and the clock is mapped to a pre-determined data lane. The bandwidth of the link in RAS mode is reduced; however, the link in the other direction can still operate normally. 16