HP DL360 The Intel processor roadmap for industry-standard servers technology - Page 9

NetBurst microarchitecture on 90nm silicon process technology

|

UPC - 613326948835

View all HP DL360 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 9 highlights

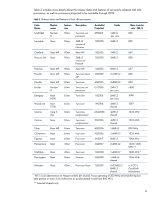

HT Technology also puts a heavier load on the OS to allocate threads and switch contexts on the device. Evaluating the threads for parallelism and context switching are OS tasks and increase the operating overhead. HT Technology presents little in the way of software licensing issues. Intel asserts that the HT design is still only a single-processor unit, so customers should not have to purchase two software licenses for each processor. This is true for Microsoft SQL Server 2000 and Windows Server 2003, which only require one license for each physical processor, regardless of the number of logical processors it contains. However, Windows 2000 Server does not make this distinction between physical and logical processors and fills the licensing limit based on the number of processors the BIOS discovers at boot. According to Intel, the system requirements for HT Technology are as follows: • A processor that supports HT Technology2 • HT Technology-enabled chipset • HT Technology-enabled system BIOS • HT Technology-enabled/optimized operating system For more information, refer to http://www.intel.com/products/ht/hyperthreading_more.htm. NetBurst microarchitecture on 90nm silicon process technology In 2004, Intel introduced major improvement to the Pentium 4 and Xeon processor lines by changing the manufacturing process from 130nm to 90nm silicon process technology and adding numerous enhancements: • Larger, more effective caches (1MB or 2-MB L2 Advanced Transfer Cache compared to 512-KB on the 0.13 micron Pentium 4 processor) • Faster processor bus: a 64-bit, 200-MHz bus capable of providing 6.4 GB/s of bandwidth by double pumping the address and quad pumping the data. The 200-MHz quad-pumped data bus is also referred to as an 800-MT/s data bus. • Extended hyper-pipeline (31 stages versus 20 stages) to enable high CPU core frequencies (described below) • Enhanced execution units including the addition of a dedicated integer multiplier, and support for shift and rotate instruction execution on a fast ALU • Improved branch prediction to help compensate for longer pipeline • Streaming SIMD Extensions 3 (SSE3) instructions (described below) • Larger execution schedulers and execution queues • Improved hardware memory prefetcher • Improved Hyper-Threading • 64-bit extensions (described below) • Two-core (for Smithfield, Dempsey, and Paxville) 2 For more information, read the white paper "Introducing the 45nm next-generation Intel® Core™ microarchitecture at Intel® 45nm Hi-k silicon technology. 9