HP DL360 The Intel processor roadmap for industry-standard servers technology - Page 4

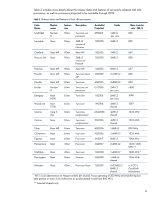

Table 2 includes more details about the release dates and features of previously released Intel x86

|

UPC - 613326948835

View all HP DL360 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 4 highlights

Table 2 includes more details about the release dates and features of previously released Intel x86 processors, as well as processors projected to be available through 2009. Table 2. Release dates and features of Intel x86 processors Code Name Market name Feature size Description Available/ Projected Cache Max. transfer rate * (MT/s) Smithfield Pentium 90nm Two-core uni- 2H2005 1MB L2 800 D processor per core Irwindale Xeon 90nm 2MB L2 1Q2005 2MB L2 800 version of Nocona Cranford Xeon MP 90nm Xeon MP 1Q2005 1MB L2 667 Prescott 2M Xeon 90nm 2MB L2 1Q2005 2MB L2 800 version of Prescott Potomac Xeon MP 90nm Xeon MP 1Q2005 8MB L3 667 Paxville Xeon MP 90nm Two-core Xeon 4Q2005 2x1MB L2 800 MP Paxville Xeon MP 90nm Two-core 4Q2005 2x2MB L2 800 Presler Pentium D 65nm Two-core uniprocessor Q12006 2MB L2 per core >800 Dempsey Xeon 5000 65nm Two-core 1H2006 2MB L2 per core 1066 Woodcrest Xeon 5100 65nm Two-core 1H2006 4MB L2 shared 1333 Conroe Core 2 Duo 65nm Two-core, uni-processor Mid-2006 4MB L2 shared 1333 MHz Conroe Xeon 65nm Two-core, uni-processor 3Q2006 4MB L2 shared 1333 MHz Tulsa Xeon MP 65nm Two-core 4Q2006 16MB L3 800 MHz Clovertown Xeon 65nm Four-core 4Q2006 2x4MB L2 1333 MHz Tigerton Xeon 65nm Four-core 2H2007 8MB L2 1066 MHz Harpertown Xeon 45nm Four-core 4Q2007 2x6MB L2 1333/1600 MHz** Wolfdale Xeon 45nm Two-core 1Q2008 1x6MB L2 1600 MHz* Dunnington Xeon 45nm Six-core 3Q2008 16MB L3 shared 1066 MHz Nehalem Xeon 45nm Four-core Xeon 1Q2009 4x256KB L2 8MB L3 shared 6.4 GT/s QuickPath Interconnect * MT/s is an abbreviation for Mega-Transfers per second. A bus operating at 200 MHz and transferring four data packets on each clock (referred to as quad-pumped) would have 800 MT/s. ** Selected chipsets only 4