Intel Pga478 Data Sheet - Page 10

Low Power Features - supported processors

|

UPC - 735858152471

View all Intel Pga478 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 10 highlights

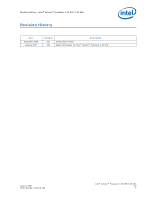

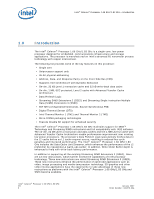

Intel® Celeron® Processor 1.66 GHz/1.83 GHz-Low Power Features 2.0 Low Power Features 2.1 Figure 1. Clock Control and Low Power States The Intel® Celeron® Processor 1.66 GHz/1.83 GHz supports the C1/AutoHALT, C1/ MWAIT, Stop Grant and Sleep states for optimal power management. C1/AutoHALT and C1/MWAIT are core-level low power states only, they do not have package-level behavior. Refer to Figure 1 for a visual representation of package level low-power states for a Intel® Celeron® Processor 1.66 GHz/1.83 GHz. The single core Intel® Celeron® Processor 1.66 GHz/1.83 GHz can enter the C1/AutoHALT/MWAIT at any time. Refer to Figure 2 for a visual representation of the core low-power states for the Intel® Celeron® Processor 1.66 GHz/1.83 GHz. Intel® Celeron® Processor 1.66 GHz/1.83 GHz implements two software interfaces for requesting low power states: the I/O mapped ACPI P_BLK register block and the Cstate extension to the MWAIT instruction. Either interface can be used at any time. The processor core presents an independent low power state request interface (ACPI P_BLK or MWAIT). Requests from the software running on the core puts into core-level low power state. The processor has logic for coordinating low power state requests from the processor core. This logic puts the Intel® Celeron® Processor 1.66 GHz/1.83 GHz into a package-level low-power state based on the highest core low power state, as desired. If the core encounters a break event while STPCLK# is asserted, it returns to C0 state by asserting the PBE# output signal. PBE# assertion signals to system logic that the processor needs to return to the Normal package-level state. This allows that core to return to the C0 state. Package-Level Low Power States Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS 10 January 2007 Order Number: 315876-002