Intel Pga478 Data Sheet - Page 7

Terminology - socket p

|

UPC - 735858152471

View all Intel Pga478 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 7 highlights

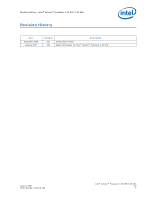

Introduction-Intel® Celeron® Processor 1.66 GHz/1.83 GHz Note: 1.1 The Intel® Celeron® Processor 1.66 GHz/1.83 GHz's 667 MHz front side bus (FSB) utilizes a split-transaction, deferred reply protocol. The FSB uses Source-Synchronous Transfer (SST) of address and data to improve performance by transferring data four times per bus clock (4X data transfer rate, as in AGP 4X). Along with the 4X data bus, the address bus can deliver addresses two times per bus clock and is referred to as a "double-clocked" or 2X address bus. Working together, the 4X data bus and 2X address bus provide a data bus bandwidth of up to 5.33 GB/second. The FSB uses Advanced Gunning Transceiver Logic (AGTL+) signaling technology, a variant of GTL+ signaling technology with low power enhancements. The processor also features the Auto Halt low power state (Extended Halt State - C1E). Intel® Celeron® Processor 1.66 GHz/1.83 GHz utilizes socketable Micro Flip-Chip Pin Grid Array (Micro-FCPGA) package technology. The Micro-FCPGA package plugs into a 478-hole, surface-mount, Zero Insertion Force (ZIF) socket, which is referred to as the mPGA478 socket. The processor supports the Execute Disable Bit capability. This feature combined with a support operating system allows memory to be marked as executable or non executable. If code attempts to run in non-executable memory the processor raises an error to the operating system. This feature can prevent some classes of viruses or worms that exploit buffer overrun vulnerabilities and can thus help improve the overall security of the system. Refer to the Intel® 64 and IA-32 Architectures Software Developer's Manuals for more detailed information. The term AGTL+ is used to refer to Assisted GTL+ signaling technology on the processor. Terminology Table 1. Terminology (Sheet 1 of 2) Term Definition A "#" symbol after a signal name refers to an active low signal, indicating a signal is in the active state when driven to a low level. For example, when RESET# is low, a reset has been requested. Conversely, when NMI is high, a non-maskable interrupt has # occurred. In the case of signals where the name does not imply an active state but describes part of a binary sequence (such as address or data), the "#" symbol implies that the signal is inverted. For example, D[3:0] = "HLHL" refers to a hex 'A', and D[3:0]# = "LHLH" also refers to a hex "A" (H= High logic level, L= Low logic level). XXXX means that the specification or value is yet to be determined. AGTL+ Advanced Gunning Transceiver Logic. Used to refer to Assisted GTL+ signaling technology on the processor The electrical interface that connects the processor to the chipset. Also referred to as Front Side Bus (FSB) the processor system bus or the system bus. All memory and I/O transactions as well as interrupt messages pass between the processor and chipset over the FSB. GTLREF A reference voltage level used on the system bus to determine the logical state of a signal. MT/s Megatransfers/second Overshoot The maximum voltage observed for a signal at the device pad, measured with respect to the buffer reference voltage. Pad The electrical contact point of a semiconductor die to the package substrate. A pad is only observable in simulations. Processor A single package that contains one complete execution core January 2007 Order Number: 315876-002 Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS 7