Intel Pga478 Data Sheet - Page 11

Core Low Power States

|

UPC - 735858152471

View all Intel Pga478 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 11 highlights

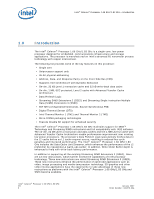

Low Power Features-Intel® Celeron® Processor 1.66 GHz/1.83 GHz Figure 2. Core Low Power States C1/ MWAIT STPCLK# asserted STPCLK# de-asserted Stop Grant STPCLK# de-asserted STPCLK# asserted STPCLK# asserted Core state break or MONITOR STPCLK# de-asserted HLT instruction MWAIT(C1) Halt break C1/Auto Halt C0 2.1.1 2.1.1.1 2.1.1.2 halt break = A20M#transition, INIT#, INTR, NMI, PREQ#, RESET#, SMI#, or APIC interrupt core state break = (halt break OR MONITOR event) AND STPCLK# high (not asserted) Core Low Power States C0 State - Normal State This is the normal operating state for the processor. C1/AutoHALT Powerdown State AutoHALT is a low power state entered when the processor executes the HALT instruction. The processor transitions to the Normal state upon the occurrence of SMI#, BINIT#, INIT#, LINT[1:0] (NMI, INTR), or an interrupt delivered over the system bus. RESET# causes the processor to immediately initialize itself. The return from a System Management Interrupt (SMI) handler can be to either Normal Mode or the AutoHALT Power Down state. Refer to the Intel® 64 and IA-32 Architectures Software Developer's Manuals in Volume 3A/3B: System Programming Guide for more information. The system can generate a STPCLK# while the processor is in the AutoHALT Power Down state. When the system deasserts the STPCLK# interrupt, the processor returns execution to the HALT state. While in AutoHALT Power Down state, the processor continues to processes system bus snoops. January 2007 Order Number: 315876-002 Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS 11