LG KU580 Service Manual - Page 24

RF Interface - reset

|

View all LG KU580 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 24 highlights

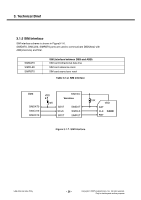

3. Technical Brief E. XGAM Subsystem The XGAM subsystem is a graphics acceleration module that provides hardware support in the creation of visual imagery and the transfer of this data to a display. The XGAM also provides support for connecting a Camera module. The visual data could be graphics, still images, or video. The XGAM subsystem is handled and provided by Ericsson. F. System Control Subsystem The SYSCON resides at the top level of the circuit architecture and is responsible for clock generation and clock and reset distribution within the digital baseband controller, as well as to external devices. The block is a slave peripheral under control of the ARM processor. The programming of the SYSCON controls the fundamental modes of operation within the digital baseband controller. Individual blocks can also be reset and their clocks held inactive by accessing the appropriate control registers. 3.1.4 RF Interface A. Asta Interface Asta controls GSM RF part using these signals through GSM RF chip-Gimli. • RF_DATA_A • RF_DATA_B • RF_DATA_C • RF_DATA_STRB Figure 3-1- 5. Schematic of Asta RF Interface B. WCDMA Radio Link Interface • RF_WCDMA_PA_0_EN • RF_WCDMA_PA_1_EN • RF_WCDMA_DCDC_EN • RF_WCDMA_PWRDET_EN Y4 RF_DATA_A AA2 RF_DATA_B Y3 RF_DATA_C Y2 RF_DATA_STRB QDATA_AMP_MSB IDATA_FREQ_MSB AMP_LSB_FREQ_LSB DCLK_DATSTR WPA0_EN TP300 WDCDC_EN WPOW_DET_EN WRX_I_N WRX_I_P WRX_Q_N WRX_Q_P WTX_I_N WTX_I_P WTX_Q_N WTX_Q_P WPOW_DET AB8 RF_WCDMA_PA_0_EN V7 RF_WCDMA_PA_1_EN AB5 RF_WCDMA_DCDC_EN AB6 RF_WCDMA_PWRDET_EN Y10 ADC_I_NEG W10 ADC_I_POS W9 ADC_Q_NEG Y9 ADC_Q_POS Y8 DAC_I_NEG W8 DAC_I_POS W7 DAC_Q_NEG Y7 DAC_Q_POS AB7 TX_POW Copyright © 2007 LG Electronics. Inc. All right reserved. Only for training and service purposes Figure 3-1-6. Schematic of WCDMA RF Interface - 25 - LGE Internal Use Only