LG KU580 Service Manual - Page 29

USB

|

View all LG KU580 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 29 highlights

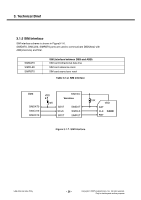

3. Technical Brief 3.1.9 USB The USB block supports the implementation of a "High-speed" device fully compliant to USB 2.0 standard. It provides an interface between the CPU (embedded local host) and the USB wire, and handles USB transactions with minimal CPU intervention. The USB specification allows up to 15 pairs of endpoints. Data for each endpoint is buffered in RAM within the USB block and is read/written from the endpoint FIFO using DMA transfers or FIFO register access. High-speed (high throughput) endpoints can use DMA while slower endpoints can use FIFO register access. The USB block can request up to six DMA channels, three for IN endpoints and three for OUT endpoints. USB Function USB_STP USB_DIR USB_CLK USB_NXT USB_DAT0 USB_DAT1 USB_DAT2 USB_DAT3 USB_DAT4 USB_DAT5 USB_DAT6 USB_DAT7 USB_CS_PD VBUS Note ULPI stop signal ULPI direction signal USB clock ULPI next signal USB data0 USB data1 USB data2 USB data3 USB data4 USB data5 USB data6 USB data7 USB chip select Power supply for Asta USB block Table 3-1-6. USB Signal Interface of Asta LGE Internal Use Only - 30 - Copyright © 2007 LG Electronics. Inc. All right reserved. Only for training and service purposes