Lenovo NetVista Technical information manual for NetVista 6269, 6568, 6569, 65 - Page 50

Lan_rstsync

|

View all Lenovo NetVista manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 50 highlights

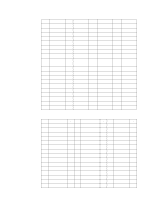

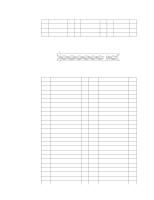

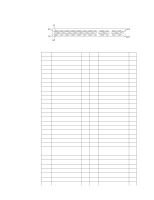

Table 23. 64-bit PCI connector-pin assignments Pin Signal I/O Pin Signal I/O A31 Address/data 18 I/O B31 +3.3 V dc A32 Address/data 16 I/O B32 Address/data 17 I/O A33 +3.3 V dc B33 C/BE 2# I/O A34 FRAME# I/O B34 Ground A35 Ground A36 TRDY# B35 IRDY# I/O I/O B36 +3.3 V dc A37 Ground B37 DEVSEL# I/O A38 STOP# I/O B38 Ground A39 +3.3 V dc B39 LOCK# I/O A40 SMBCLK1 I/O B40 PERR# I/O A41 SMBDATA1 I/O B41 +3.3 V dc A42 Ground B42 SERR# I/O A43 PAR B43 +3.3 V dc A44 Address/data 15 I/O B44 C/BE 1# I/O A45 +3.3 V dc I/O B45 Address/data 14 I/O A46 Address/data 13 B46 Ground A47 Address/data 11 I/O B47 Address/data 12 I/O A48 Ground I/O B48 Address/data 10 I/O A49 Address/data 9 A50 Key B49 Ground B50 Key A51 Key B51 Key A52 C/BE(0)# I/O B52 Address/data 8 I/O A53 +3.3 V dc I/O B53 Address/data 7 I/O A54 Address/data 6 B54 +3.3 V dc A55 Address/data 4 I/O B55 Address/data 5 I/O A56 Ground I/O B56 Address/data 3 I/O A57 Address/data 2 B57 Ground A58 Address/data 0 I/O B58 Address/data 1 I/O A59 +5 V dc B59 +5 V dc A60 ACK64# I/O B60 ACK64# I/O A61 +5 V dc B61 +5 V dc A62 +5 V dc A63 TXD0 B62 +5 V dc B63 RXD0 A64 TXD1 B64 RXC1 A65 TXD2 B65 RXD2 A66 LAN_CLK I/O B66 LAN_RSTSYNC A67 Ground A68 EE_DOUT B67 Ground B68 EE_SHCLK 40 NetVista™ Technical Information Manual