MSI A55M User Guide - Page 127

此项用来设置 TWCL WriTe CAS LaTencY 时序。

|

View all MSI A55M manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 127 highlights

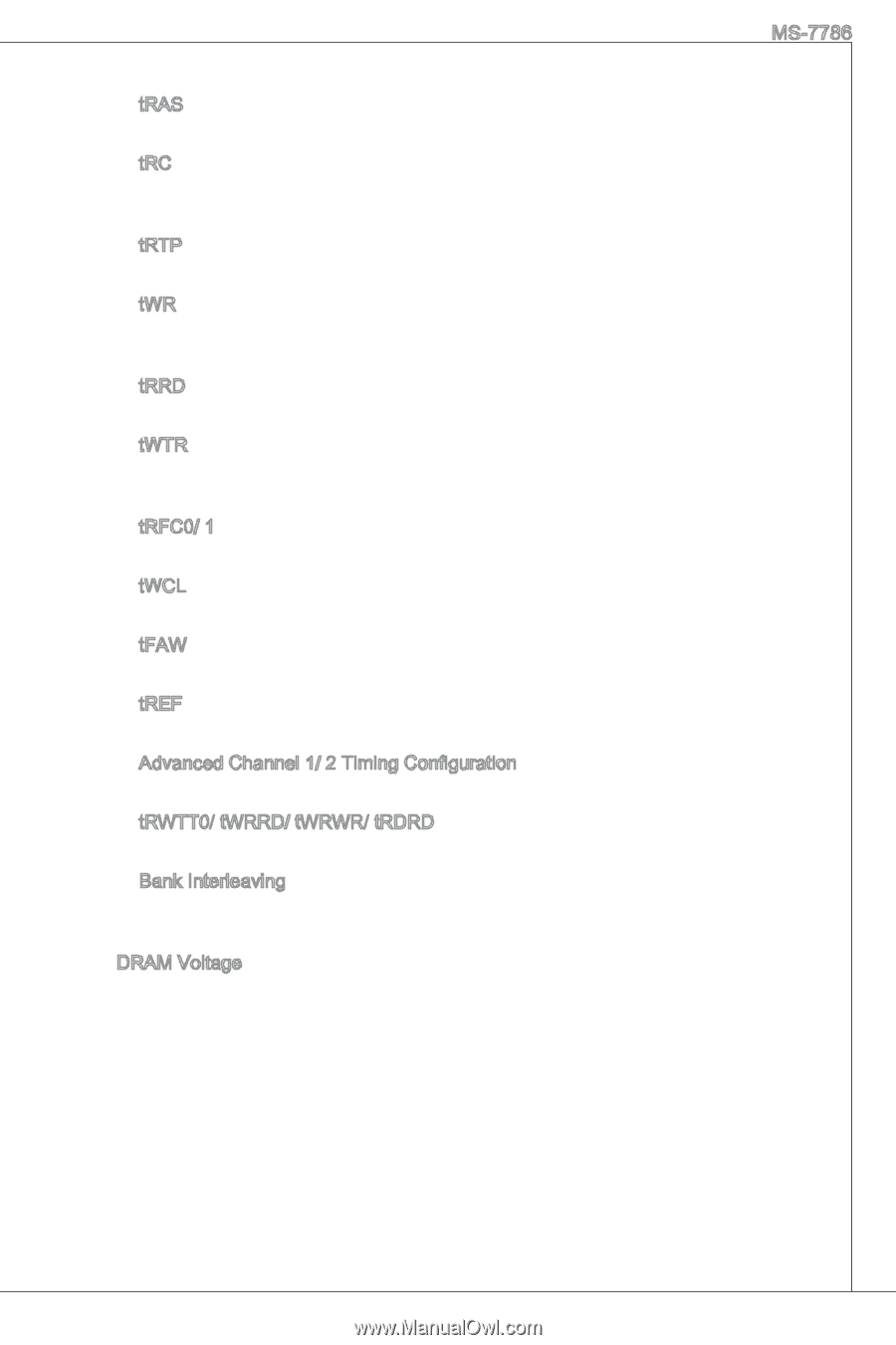

MS-7786 tRAS RAS tRC tRTP tWR tRRD Specifies the active-to-active delay of different banks. tWTR I/O tRFC0/ 1 RFC0/1 tWCL tWCL (Write CAS Latency) 时序。 tFAW tFAW (four activate window delay) 时序。 tREF tREF (refresh rate) 时序。 Advanced Channel 1/ 2 Timing Configuration 按

±27

MS-7786

TRAS

此设置决定了 RAS 由读取到写入内存所需时间。

TRC

行周期时间决定了完成一个完整的循环所需的最小周期数,也就是从行激活到

行充电的时间

TRtP

此项指定读指令和预充电之间的时间间隔。

TWR

最后一次写操作和下一次开始预充电操作之间的最小时间间隔,允许感觉线路

恢复核心数据。

TRRD

Specifies THe acTive-To-acTive delaY of differenT banks.

TWtR

最后一次有效写操作和下一次开始读操作之间的最小时间间隔。允许I/O在读命

令开始前超速感觉线路。

TRFC0/ ±

此项设置决定了 RFC0/± 从存储单元读取和写入所花费的时间。

TWCL

此项用来设置 TWCL (WriTe CAS LaTencY) 时序。

TFAW

此项用来设置 TFAW (four acTivaTe window delaY) 时序。

TREF

此项用来设置 TREF (refresH raTe) 时序。

Advanced CHannel ±/ 2 timing ConfiguraTion

按 <EnTer> 进入子菜单。并且你可以为每个通道设置高级内存时序。

TRWtt0/ TWRRD/ TWRWR/ TRDRD

此项用来为通道 ±/ 2 设置内存时序。

Bank InTerleaving

对提升内存超频性能来说,存储器组交错是一个重要参数。它允许系统同时存

取多个存储器组。

DRAM VolTage

此选项用来调整内存电压。