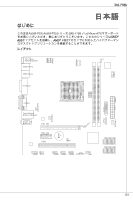

MSI A55M User Guide - Page 147

本項設定 TWCL WriTe CAS LaTencY 時序。

|

View all MSI A55M manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 147 highlights

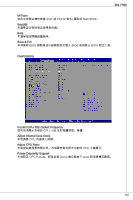

MS-7786 tRAS RAS tRC tRTP tWR sense amplifier tRRD active-to-active tWTR tRFC0/ 1 RFC0/1 tWCL tWCL (Write CAS Latency) 時序。 tFAW tFAW (four activate window delay) 時序。 tREF tREF (refresh rate) 時序。 Advanced Channel 1/ 2 Timing Configuration 按下

±47

MS-7786

TRAS

本項指定 RAS 由讀取到寫入記憶體所需時間。

TRC

本項是記憶體由列活化到預充電整個所需的最小週期。

TRtP

本項設定讀取到預充電間的間隔時間。

TWR

本項是寫入資料結束到預充電指令開始間的最短間距。本項透過感覺放大器

(sense amplifier)回復資料。

TRRD

本項設定不同記憶體分組之間 (acTive-To-acTive) 的延遲時脈。

TWtR

本項是寫入資料脈衝結束到列讀取指令開始間的最短時間。輸出入閘道會先驅

動感覺放大器,再開始讀取指令。

TRFC0/ ±

本項決定 RFC0/± 由記憶體讀取及寫入記憶體所需時間。

TWCL

本項設定 TWCL (WriTe CAS LaTencY) 時序。

TFAW

本項設定 TFAW (four acTivaTe window delaY) 時序。

TREF

本項設定 TREF (refresH raTe) 時序。

Advanced CHannel ±/ 2 timing ConfiguraTion

按下 <EnTer> 鍵以進入子選單。接著可在各個通道設定進階記憶體時序。

TRWtt0/ TWRRD/ TWRWR/ TRDRD

這些選項設定記憶體通道 ±/ 2 的記憶體時序。

Bank InTerleaving

本項是在記憶體超頻時提升效能的重要參數,可讓系統同時於不同記憶體分組

之間作存取。

DRAM VolTage

本項設定記憶體電壓。