MSI E7500 User Manual - Page 9

Mainboard Specification - cpu

|

View all MSI E7500 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 9 highlights

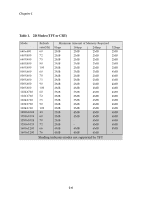

Chapter 1 Mainboard Specification Target Segment Target in the entry-level and mid-range, front-end and general purpose server market segments CPU The second-generation of microprocessors using the Intel® NetBurst™ microarchitecture Supports Single/Dual Intel® Xeon™ w/ 512KB L2 cache processors Feature L2 Cache L3 Cache Data Bus Transfer Rate Multi-Processor Support Manageability Features Package Operating Voltage Prestonia 512 KB None 3.2 GB/s 1.2 CPUs Intel and OEM EEPROMS and thermal sensor on package PGA 603 1.475 V Chipset Intel E7500 Chipset - Intel ICH 3-S (I/O Controller) - MCH (Memory Controller Hub) - P64H2 (64-bit I/O Hub) System Bus Feature - Intel's first generation server chipset designed for use with the Xeon processor - Supports dual processors at 400 Mn/s - System bus bandwidth of 3.2 GB/s - Supports 36-bit system bus addressing model - 12 deep in-order queue, 2 deep defer queue Memory Bus Feature 144-bit wide, DDR-200 memory interface memory bandwidth of 3.2 GB/s Supports ECC registered DDR-200 DIMMs Supports a maximum of 12 GB of memory 1-2