HP DL360 Memory technology evolution: an overview of system memory technologie - Page 3

data bit at a time. The throughput bandwidth of the data bus depends on its width in bits and its

|

UPC - 613326948835

View all HP DL360 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 3 highlights

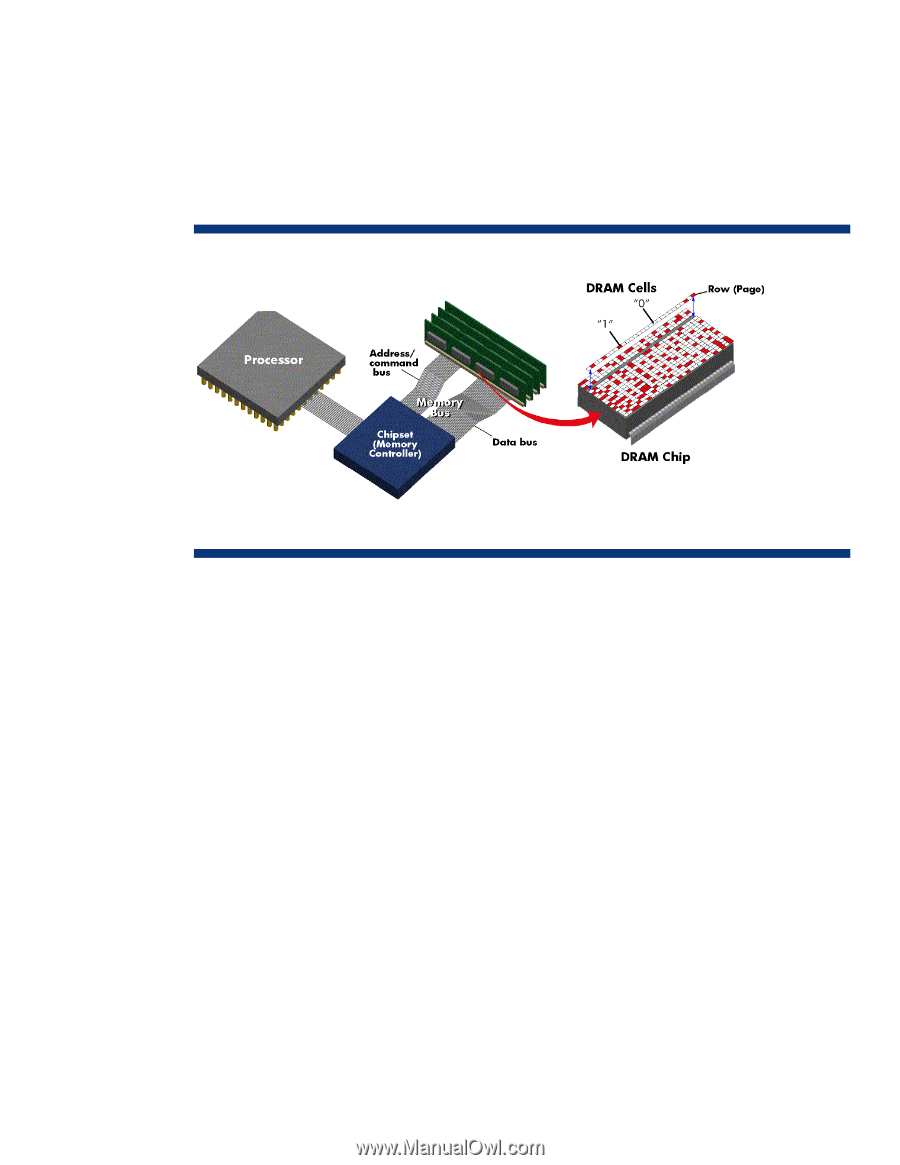

Each DRAM chip contains millions of memory locations (or cells), which are arranged in a matrix of rows and columns (Figure 1). Peripheral circuitry on the DIMM reads, amplifies, and transfers the data from the memory cells to the memory bus. Each DRAM row, called a page, consists of several DRAM cells. Each DRAM cell on a page contains a capacitor capable of storing an electrical charge for a very short time. A charged cell represents a "1" data bit, and an uncharged cell represents a "0" data bit. To prevent the capacitors from discharging, they must be recharged (refreshed) thousands of times per second to maintain the validity of the data. Refresh mechanisms are described later in this section. Figure 1. Representation of a single DRAM chip on a DIMM NOTE: Some CPU designs have the memory controller function integrated into processor module The memory subsystem operates at the memory bus speed. Typically, to access a DRAM cell, the memory controller sends electronic address signals that specify the row address and column address of the target cell. The memory controller sends these signals to the DRAM chip by way of the memory bus. The memory bus consists of two sub-buses: the address/command bus and the data bus. The data bus is a set of lines (traces) that carry the data to and from DRAM. Each trace carries one data bit at a time. The throughput (bandwidth) of the data bus depends on its width (in bits) and its frequency. The data width of a memory bus is usually 64-bits, which means that the bus has 64 traces, each of which transports one bit at a time. Each 64-bit unit of data is called a data word. The address portion of the address/command bus is a set of traces that carry signals identifying the location of data in memory. The command portion of the address/command bus conveys instructions such as read, write, or refresh. 3