HP DL360 Memory technology evolution: an overview of system memory technologie - Page 9

DIMMs or four single rank DIMMs. If two dual-rank DIMMs are installed, then the last two slots must

|

UPC - 613326948835

View all HP DL360 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 9 highlights

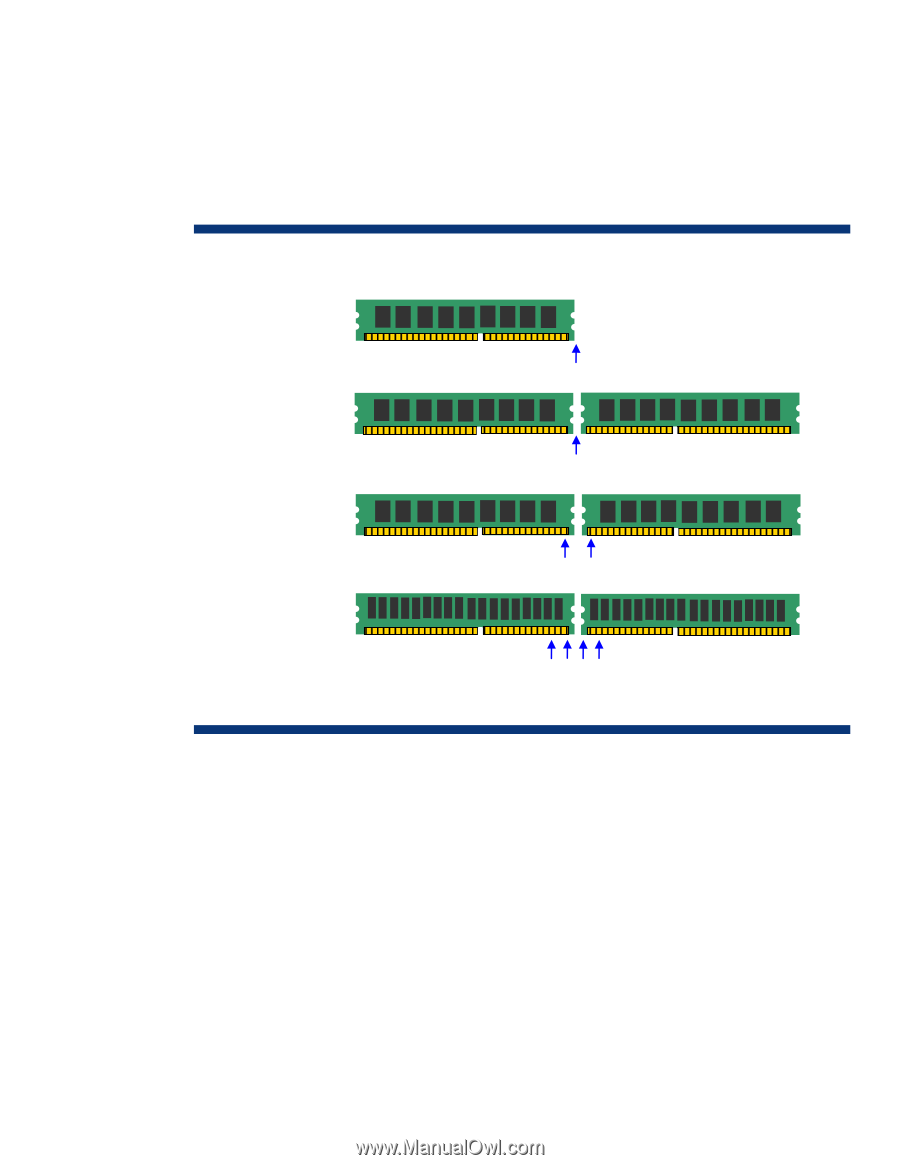

A single-rank ECC DIMM (x4 or x8) uses all of its DRAM chips to create a single block of 72 bits, and all the chips are activated by one chip-select (CS) signal from the memory controller (top two illustrations in Figure 7). A dual-rank ECC DIMM produces two 72-bit blocks from two sets of DRAM chips on the DIMM, requiring two chip-select signals. The chip-select signals are staggered so that both sets of DRAM chips do not contend for the memory bus at the same time. Quad-rank DIMMs with ECC produce four 72-bit blocks from four sets of DRAM chips on the DIMM, requiring four chip-select signals. Like the dual-rank DIMMs, the memory controller staggers the chip-select signals to prevent the four sets of DRAM chips from contending for the memory bus at the same time. Figure 7. Single-sided and double-sided DDR SDRAM DIMMs and corresponding DIMM rank Single-sided, single-rank Double-sided, single-rank Side 1(only), 8b DRAM x9 72b CS Side 1, 4b DRAM x9 72b CS Side 2, 4b DRAM x9 Double-sided, dual-rank Side 1, 8b DRAM x9* 72b CS (2) Side 2, 8b DRAM x9* Double-sided, quad-rank Side 1, 8b DRAM x18* * Actual DRAM configuration can vary depending on DRAM density and configuration 72b CS (4) Side 2, 8b DRAM x18* Memory ranks are not new, but their role has become more critical with the advent of new chipset and memory technologies and growing server memory capacities. Dual-rank DIMMs improve memory density by placing the components of two single-rank DIMMs in the space of one module. The chipset considers each rank as an electrical load on the memory bus. At slower bus speeds, the number of loads does not adversely affect bus signal integrity. However, for faster memory technologies such as DDR2-667, there is a maximum number of ranks that the chipset can drive. For example, if a memory bus on a server has four DIMM slots, the chipset may only be capable of supporting two dual-rank DIMMs or four single rank DIMMs. If two dual-rank DIMMs are installed, then the last two slots must not be populated. To compensate for the reduction in the number of DIMM slots on a bus at higher speeds, modern chipsets employ multiple memory buses. If the total number of ranks in the populated DIMM slots exceeds the maximum number of loads the chipset can support, the server may not boot properly or it may not operate reliably. Some systems check the memory configuration while booting to detect invalid memory bus loading. When an invalid memory configuration is detected, the system stops the boot process to avoid unreliable operation. 9