Brother International HL 760 Service Manual - Page 12

Dt79r304, °-°, Dataend, Bcntd, Sysclk, Reset, Sclk2, Clk2x, Cpuintn3, Intn4, Crdce, Brcond0, Brcond

|

UPC - 012502562832

View all Brother International HL 760 manuals

Add to My Manuals

Save this manual to your list of manuals |

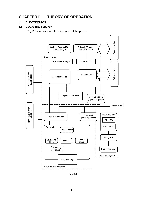

Page 12 highlights

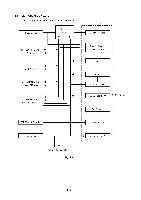

1.3 Main PCB 1.3.1 CPU Core Fig. 2.3. shows the CPU circuit block on the main PCB. The CPU is a I DT 79R3041-20J which is driven with a clock frequency of 20 MHz. This clock frequency is made by dividing the source clock of 40.0 MHz into two. The address and data bus are 32 bits of ADO to AD31. The total memory space is 4 Gbytes. #111 I DT79R304 I -20J VCC°-°- 5 13 VCC VCC 22 VCC 32 VCC 42 VCC 50 VCC 57 VCC 66 VCC 73 VCC 82 ycc DATAEND 4 NRD 53 RD D 45 AW D 4 BCNTD 39 6 VSS 12 VSS 21 VSS 31 VSS 41 VSS 49 VSS 58 VSS 65 VSS 74 VSS R67 330 SYSCLK DA ALE 46 A2 51 A3 62 01, 3-a-li- VSS 38 C RESET AD00 AD01 54 55 AD02 56 (03-07F) SCLK2 14 CLK2x IN AD03 59 CPUI NTN0 27 C S INTO AD04 60 61 ADM +6 \I° CPUI NTNI CPUI NTN2 CPUINTN3 26 C SINT I 25 C N 24 CI T3 R39 CPU INTN4 4( 3.A., 23 CTN7 20 CT7S AD06 62 AD07 AD08 63 B4 67 AD09 AD10 AD11 68 69 35 CRDCE AD12 70 71 36 CTER AD13 AD14 72 HAee 34 C BRED ADIS 75 76 103 5,- - -, 4 +5V3-.- ,•--L-g7-..W_ _ _i j2 gi I I 33 BRCOND0 ?..0__ BRCOND I ADIS AD17 AD18 77 78 2823- SBRCOND2 AD19 79 80 SBRCOND3 AD20 An 103 AD21 83 +5 R56 ,\."."., 7 c BERR AD22 84 1 47 D I AGO 48 n 1Aci AD23 AD24 2 3 AD2S 19 RSVD0 18 RSvD1 AD26 AD27 AD28 4 7 8 17 RSVD2 16 RSVD3 15 RSVD4 AD29 AD30 AD3 I 9 1 0 1 1 AD00 AD01 AD02 AD03 AD04 ADDS AD06 AD07 AD08 AD09 AD10 ADI1 AD12 AD13 AD14 ADIS AD16 AD17 ADIS AD19 AD20 AD21 AD22 AD23 AD24 AD25 AD26 AD27 AD28 AD29 AD30 AD31 Fig. 2.3 II - 3