LG KM710 Service Manual - Page 15

HW Circuit Description - bands

|

View all LG KM710 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 15 highlights

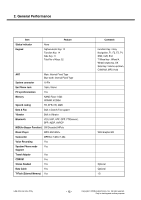

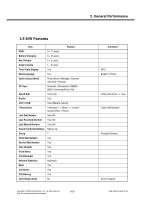

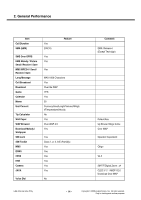

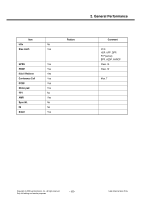

3. HW Circuit Description 3. HW Circuit Description 3.1 General Description The RF part consists of a transmitter, a receiver, a synthesizer, a voltage supply and a DCXO part. The main RF Chipset B6PLD is a highly integrated RF transceiver IC FOR Digital Interface of GSM 850,DCS1800 and PCS1900 quad-band cellular systems. The B6PLD incorporates EDGE transceiver capability, quad R low-noise amplifiers (LNAs). Direct conversion mixers, a programmable gain amplifier(PGA) with DC offset and frequency response correction, ADC, Digital filter, Digital Interface, fully integrated VCOs, an RF fractional-N synthesizer, a low-noise offset PLL transmitter, Digital modulator, TXDAC, RAMPDAC, and AFCDAC. The B6PLD includes state machine control through serial programming. All functions operate down to 2.67V and are housed in a 72- pin BGA package. Hence the B6PLD can form a small size transceiver handset for quad band EDGE transceiver. 3.2 RF Part 3.2.1 Receiver Part The B6PLD receiver supports quad band, so the front-end incorporates four LNAs and two mixers. The incoming RF signals are mixed directly down to I/Q baseband by the front-end block. This incorporates four LNAs/four buffers and two Gilbert Cell mixer blocks optimized for operation at 850MHz, 900MHz, 1800MHz and 1900MHz respectively. The front-end block is followed by two closely matched baseband amplifier chains. These include distributed low pass filtering, one switched gain stage and one fixed gain stage. In addition, the baseband section integrates A/D and D/A converters which provide automatic on-chip correction of DC offsets. LGE Internal Use Only Receiver Part Block Diagram - 16 - Copyright © 2008 LG Electronics. Inc. All right reserved. Only for training and service purposes