LG KM710 Service Manual - Page 16

Baseband PGA/Low pass Filter Specifications, 2.1.2 DC offset auto-calibration system

|

View all LG KM710 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 16 highlights

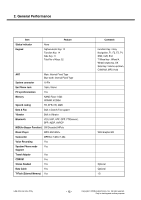

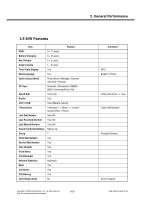

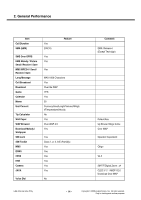

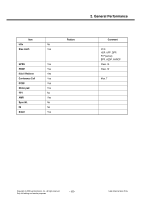

3. HW Circuit Description 3.2.1.1 Baseband PGA/Low pass Filter Specifications The baseband programmable amplifier comprises one stage with variable gain followed by a fixed gain amplifier. The overall gain control range is 36dB with 6dB Steps. The filtering is provided by a single R/C low pass filter with an on-chip capacitor followed by on-chip Chebychev low pass filters. The filters have been specified to achieve maximal group delay flatness in the pass-band combined with the required levels of suppression of interfering signals. The distribution of the gain and filtering has been designed to ensure that the receiver does not compress under blocking conditions. The final fixed gain amplifier is included to match the on-chip levels to the input dynamic range of the ADC. 3.2.1.2 DC offset auto-calibration system B6PLD implements a system for cancelling the DC offsets in the baseband programmable gain amplifiers(PGA). This prevents a small DC offset at the input giving a large DC offset at the output, even at high gain settings. When the B6PLD receiver is performing an auto-calibration, the sequencer cancels the offsets locally around the PGA, then the Digital filter. The system includes switches to short out the signal path whilst the cancellation is occurring. The switches are opened in sequence as the calibration progresses. For PGA the A/D converter system employs a successive approximation technique and achieves 6 bit resolution. The PGA stage has an associated 6 bit current DAC which cancels the DC offset at the output. The sequencer ensures that on-chip filters have sufficient time to settle before applying correction in the next digital offset cancellation stage. Copyright © 2008 LG Electronics. Inc. All right reserved. Only for training and service purposes - 17 - LGE Internal Use Only