LG KM710 Service Manual - Page 38

Pin Description

|

View all LG KM710 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 38 highlights

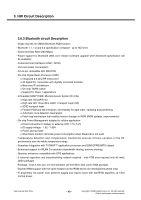

3. HW Circuit Description 3.6.2 Pin Description Pin Description CLOCKS/GLOBAL SIGNALS SLOW-CLK_IN 32.768.kHz clock input XTALM Negative fast crystal in XTALP/FAST_CLK_IN Positive fast crystal in/fast clock input RADIO FREQUENCY INTERFACE RFP Receiver/transmit differential RF I/O RFM Receiver/transmit differential RF/IO POWER MANAGEMENT VLDC_OUT Very-low drop-output voltage KA_OUT Keep alive output NSHUT_DOWN Devices shutdown input(active low) also acts as power-on reset POWER SUPPLY VBAT Battery power supply VDD_IO1 Power supply for I/O BB_LDO_OUT1 Baseband LDO output ANA_LDO_OUT Analog LDO output RFIO_LDO_OUT RFIO LDO output, power source for RF elements OSC_LDO_OUT OSC LDO output VDD_IN_BB Baseband LDO input voltage BGAP_V BGAP reference voltage BGAP_I BGAP reference current(used only for test) GROUND VSS Digital ground VSSA Analog ground/RF analog ground I/O NAME AUD_CLK Input-when external codec is configured as master(default configuration) AUD_FSYNC AUD_IN AUD_OUT High Z with PD, except when transmitting voice samples GPIO0 EXT_CLK_REQ_OUT GPIO1 EXT_CLK_REQ_IN HCI UART INTERFACE HCI_RX HCI UART data receive HCI_TX HCI UART data transmit Copyright © 2008 LG Electronics. Inc. All right reserved. Only for training and service purposes - 39 - LGE Internal Use Only