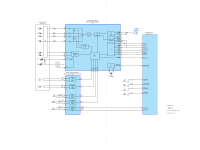

Sony CDX-M800 Service Manual - Page 20

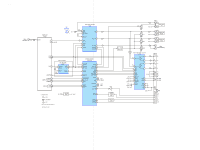

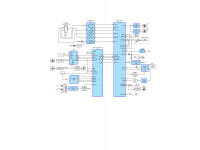

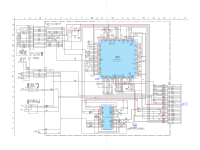

M30833fjgp-066 Display System Control Display Board - serial

|

View all Sony CDX-M800 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 20 highlights

CDX-M800 • IC2 M30833FJGP-066 (DISPLAY SYSTEM CONTROL) (DISPLAY Board) Pin No. Pin Name I/O Pin Description 1 SYS RST I Main chip enable input 2 NC I Not used. (Open) 3 FL DATA3 O FL serial data output 4 NC O Not used. (Open) 5 FL CLK IN I FL serial clock input 6 BYTE I L fixed terminal 7 CNVSS I Flash write-in signal input 8 NC O Not used. (Open) 9 NC O Not used. (Open) 10 RESET I CPU reset signal input 11 XOUT O Main clock signal output (30MHz) 12 VSS - Ground 13 XIN I Main clock signal input (30MHz) 14 VCC - Power supply pin (+5V) 15 NMI I Non maskable interrupt signal input 16 NC O Not used. (Open) 17 NC O Connecting to pin 20. 18 NC O Not used. (Open) 19 NC O Not used. (Open) 20 NC O Connecting to pin 17. 21 LAT O FL data LAT output 22 BK O FL BK output 23 GCP2 O FL GCP2 outpit 24 NC O Not used. (Open) 25 GCP1 O FL GCP1 output 26 NC O Not used. (Open) 27 GCP4 O FL GCP4 output 28 GCP3 O FL GCP3 output 29 SYS SO O Main BUS data output 30 SYS SI I CPU BUS data input 31 SYS CLK O Main BUS clock input 32 NC O Not used. (Open) 33 FL DAT1 O FL serial data output 34 NC O Not used. (Open) 35 FL CLK O FL serial clock output 36 LCD CE O LCD driver chip enble output 37 LCD INH O LCD driver inhibit output 38 NC O Not used. (Open) 39 HOLD I Flash write-in signal input 40 - 43 NC O Not used. (Open) 44 WRI/WR I Flash write-in signal input 45 - 59 NC O Not used. (Open) 60 VCC O Power supply pin (+5V) 61 NC O Not used. (Open) 62 VSS O Ground 63 - 93 NC O Not used. (Open) 94 AVSS - Ground 95 NC O Not used. (Open) 96 VREF - Power supply pin (+5V) 97 AVCC - Power supply pin (+5V) 98 RXD1 - Not used. (Open) 99 FL DATA2 O FL serial data output 100 FL CLK IN I FL serial clock input 20