Sony MDSJE320 Service Manual - Page 42

Pin No., Pin Name, Function

|

UPC - 027242541344

View all Sony MDSJE320 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 42 highlights

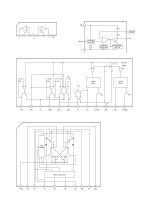

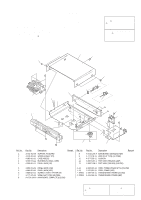

• IC307 A/D, D/A converter (CXD8607N) Pin No. Pin Name I/O 1 INRP I 2 INRM I 3 REFI I 4 AVDD - 5 AVss - 6 APD I 7 NU - 8 NU - 9 TEST1 I 10 LRCK1 I 11 BCK1 I 12 ADDT O 13 V35A - 14 VSS1 (LF) - 15 MCKI I 16 DPD I 17 VSS2 (LF) - 18 INIT I 19 MODE I 20 SHIFT I 21 LATCH I 22 256CK O 23 V35D - 24 VSS2 - 25 512CK O 26 BCK2 I 27 DADT I 28 LRCK2 I 29 VDD2 - 30 R1 O 31 AVDDR - 32 R2 O 33 AVSSR - 34 XVDD - 35 XOUT O 36 XIN I 37 XVSS - 38 AVSSL - 39 L2 O 40 AVDDL - Function Rch analog (+) input Rch analog (-) input A/D reference voltage input (+3.2V) +5V power supply (A/D, analog) Ground (A/D, analog) A/D analog block power down "L": Power down Not used Test pin (Fixed at "L") A/D LRCK input A/D BCK input A/D data output +3.3V power supply Ground (A/D, digital) A/D master clock input (256 fs) A/D digital block power down "L": Power down/reset Ground (D/A, digital) D/A initialize "L": Initialize Mode flag input Shift clock input Latch clock input 256 fs clock output +3.3V power supply Ground (D/A, digital) 512 fs clock output D/A BCK input D/A data input D/A LRCK input +5V power supply (D/A, digital) Rch PLM output 1 +5V power supply (D/A, Rch, analog) Rch PLM output 2 Ground (D/A, Rch, analog) +5V power supply (X'tal) X'tal oscillation output (22 MHz) X'tal oscillation input (512 fs ) (22 MHz) Ground (X'tal) Ground (D/A, Lch, analog) Lch PLM output 2 +5V power supply (D/A, Lch, analog) - 58 -