Intel DH61AG Technical Product Specification - Page 57

Table 31., Pin LVDS Connector

|

View all Intel DH61AG manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 57 highlights

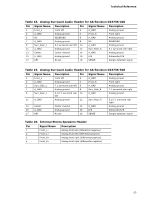

Technical Reference Table 31. 40-Pin LVDS Connector Pin Signal Name 1 ODD_Lane3_P 2 ODD_Lane3_N 3 ODD_Lane2_P 4 ODD_Lane2_N 5 ODD_Lane1_P 6 ODD_Lane1_N 7 ODD_Lane0_P 8 ODD_Lane0_N 9 EVEN_Lane3_P 10 EVEN_Lane3_N 11 EVEN_Lane2_P 12 EVEN_Lane2_N 13 EVEN_Lane1_P 14 EVEN_Lane1_N 15 EVEN_Lane0_P 16 EVEN_Lane0_N 17 EDID_GND 18 LCD_VCC (3.3 V/5 V/12 V) 19 LCD_VCC (3.3 V/5 V/12 V) 20 LCD_VCC (3.3 V/5 V/12 V) Pin 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 Signal Name N/C EDID_3.3 V LCD_GND LCD_GND LCD_GND ODD_CLK_P ODD_CLK_N BKLT_GND BKLT_GND BKLT_GND EDID_CLK BKLT_ENABLE BKLT_PWM_DIM EVEN_CLK_P EVEN_CLK_N BKLT_PWR (12 V/19 V) BKLT_PWR (12 V/19 V) BKLT_PWR (12 V/19 V) N/C EDID_DATA NOTE LVDS single-channel output is driven from the ODD signals. 57