eMachines E644G eMachines E644 and E644G Series Serivce Guide - Page 157

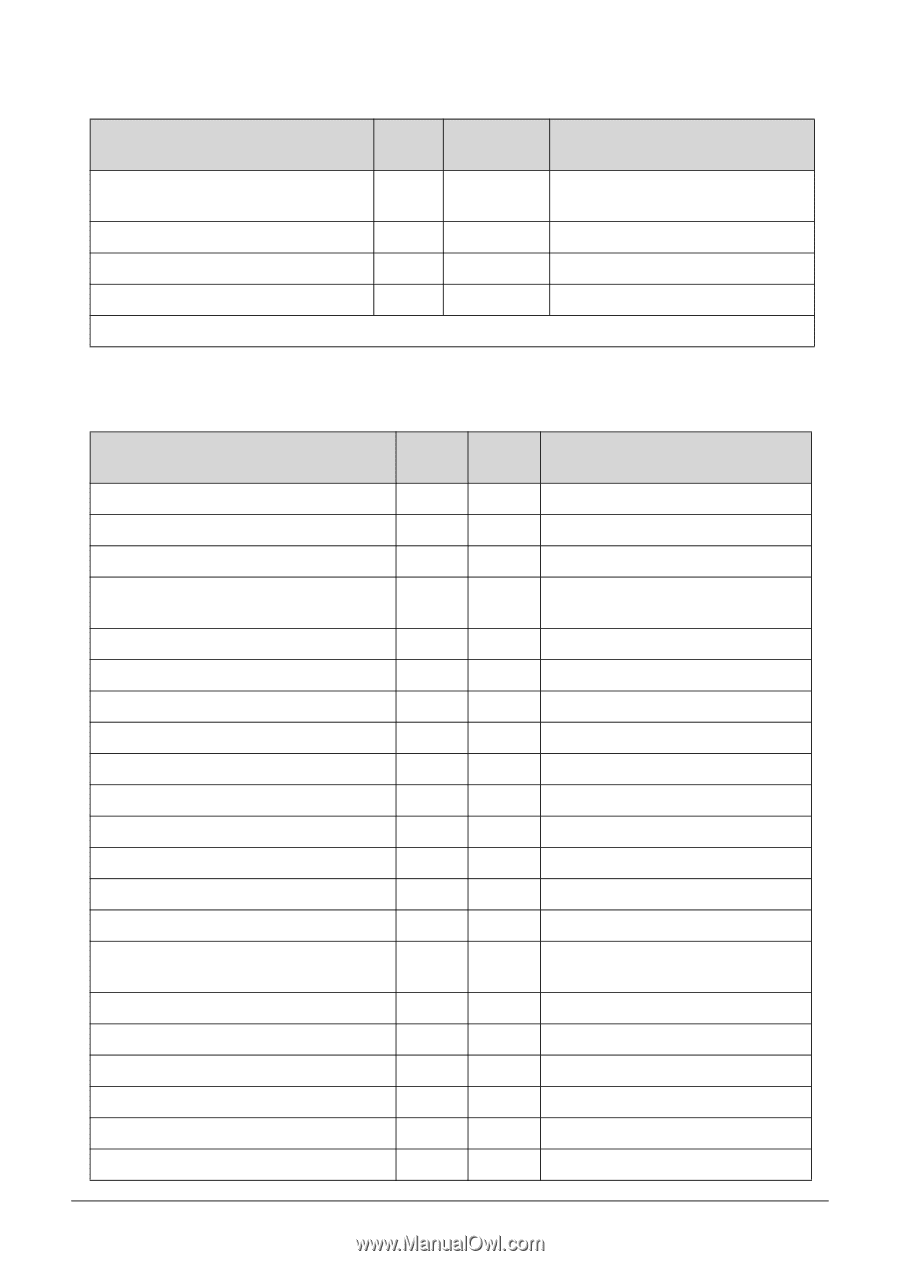

Table 4-5., DXE Phase POST Code Table, Functionality Name Include, PostCode.h, Phase, Description

|

View all eMachines E644G manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 157 highlights

Table 4-4. (Continued)PEI Phase POST Code Table Functionality Name (Include\ PostCode.h) Phase Post Code Description PEI_RECOVERY_START_FLASH PEI 88 Start Flash BIOS with Recovery image PEI_ENTER_DXEIPL PEI 89 Loading BIOS image to RAM PEI_FINDING_DXE_CORE PEI 8A Loading DXE core PEI_GO_TO_DXE_CORE PEI 8B Enter DXE core * 3rd party relate functions - Platform dependence. Table 4-5. DXE Phase POST Code Table Functionality Name (Include\ PostCode.h) Phase Post Code DXE_TCGDXE* DXE 40 DXE_SB_SPI_INIT* DXE 41 DXE_CF9_RESET* DXE 42 DXE_SB_SERIAL_GPIO_INIT* DXE 43 DXE_SMMACCESS* DXE_SIO_INIT* DXE_LEGACY_REGION* DXE_SB_INIT* DXE_IDENTIFY_FLASH_DEVICE* DXE_FTW_INIT DXE_VARIABLE_INIT DXE_VARIABLE_INIT_FAIL DXE_MTC_INIT DXE_CPU_INIT DXE_MP_CPU_INIT DXE 44 DXE 46 DXE 47 DXE 48 DXE 49 DXE 4A DXE 4B DXE 4C DXE 4D DXE 4E DXE 4F DXE_SMBUS_INIT DXE_SMART_TIMER_INIT DXE_PCRTC_INIT DXE_SATA_INIT* DXE_SMM_CONTROLER_INIT* DXE_LEGACY_INTERRUPT* DXE 50 DXE 51 DXE 52 DXE 53 DXE 54 DXE 55 Description TPM initial in DXE South bridge SPI initialization Setup Reset service South bridge Serial GPIO initialization Setup SMM ACCE SS service Super I/O DXE initialization Setup Legacy Region service South Bridge Middle initialization Identify Flash device Fault Tolerant Write verification Variable Service initialization Fail to initial Variable Service MTC Initial CPU Middle Initialization Multi-processor Middle Initialization SMBUS Driver Initialization 8259 Initialization RTC Initialization SATA Controller early Initialization Setup SMM Control service Setup Legacy Interrupt service Troubleshooting 4-23