Acer Aspire 9500 Service Guide - Page 81

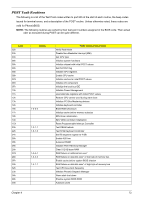

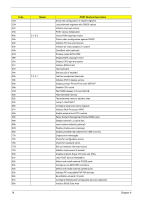

Beeps, For Boot Block in ROM, POST Routine Description, Initialize system I/O

|

View all Acer Aspire 9500 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 81 highlights

Code C7h C8h C9h D2h Beeps POST Routine Description Initialize notebook docking late Force check (optional) Extended checksum (optional) Unknown interrupt Code E0h E1h E2h E3h E4h E5h E6h E7h E8h E9h EAh EBh ECh EDh EEh EFh F0h F1h F2h F3h F4h F5h F6h F7h Beeps 1 For Boot Block in ROM Initialize the chipset Initialize the bridge Initialize the CPU Initialize system timer Initialize system I/O Check force recovery boot Checksum BIOS ROM Go to BIOS Set Huge Segment Initialize Multi Processor Initialize OEM special code Initialize PIC and DMA Initialize Memory type Initialize Memory size Shadow Boot Block System memory test Initialize interrupt vectors Initialize Run Time Clock Initialize video Initialize System Management Mode Output one beep before boot Boot to Mini DOS Clear Huge Segment Boot to Full DOS 76 Chapter 4