Asus KFN4-D16 User Guide - Page 78

CPU Configuration, 4.2 Chipset

|

UPC - 610839141265

View all Asus KFN4-D16 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 78 highlights

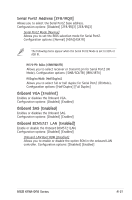

4.4.1 CPU Configuration The items in this menu show the CPU-related information that the BIOS automatically detects. CPU Configuration Module Version: 00.00 Physical Count: 1 Logical Count : 2 AMD Opteron(tm) Processor 146 Revision: F1 Cache L1: 128KB Cache L2: 2048KB Speed : 2400MHz Current FSB Multiplier: 12x Maximum FSB Multiplier: 12X Able to Change Freq : Yes uCode Patch Level : None Required GART Error Reporting MTRR Mapping Runtime Legacy PSB ACPI 2.0 Objects [Disabled] [Continuous] [Disabled] [Enabled] This option should remain disabled for the normal operation. The driver developer may enable it for testing purpose. GART Error Reporting [Disabled] Enables or disables the GART Error reporting feature. Configuration options: [Disabled] [Enabled] MTRR Mapping [Continuous] Sets the method used for programming CPU MTRRs when 4GB or more memory is installed on the system. When set to Discrete, the BIOS leaves the PCI hole below the 4GB boundary undescribed. Set to Continuous to describe the PCI hole as non-cacheable. Configuration options: [Continuous] [Discrete] ACPI 2.0 Objects [Enabled] Enables or disables generation of the ACPI 2.0 objects. Configuration options: [Disabled] [Enabled] 4.4.2 Chipset The Chipset menu allows you to change the advanced chipset settings. Select an item then press to display the sub-menu. Advanced Chipset Settings WARNING: Setting wrong values in below sections may cause system to malfunction. NorthBridge Configuration SouthBridge Configuration Hyper Transport Configuration Options for NB. ASUS KFN4-D16 Series 4-17