Sony MZ-R50 Service Manual - Page 35

Diagrams - description

|

View all Sony MZ-R50 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 35 highlights

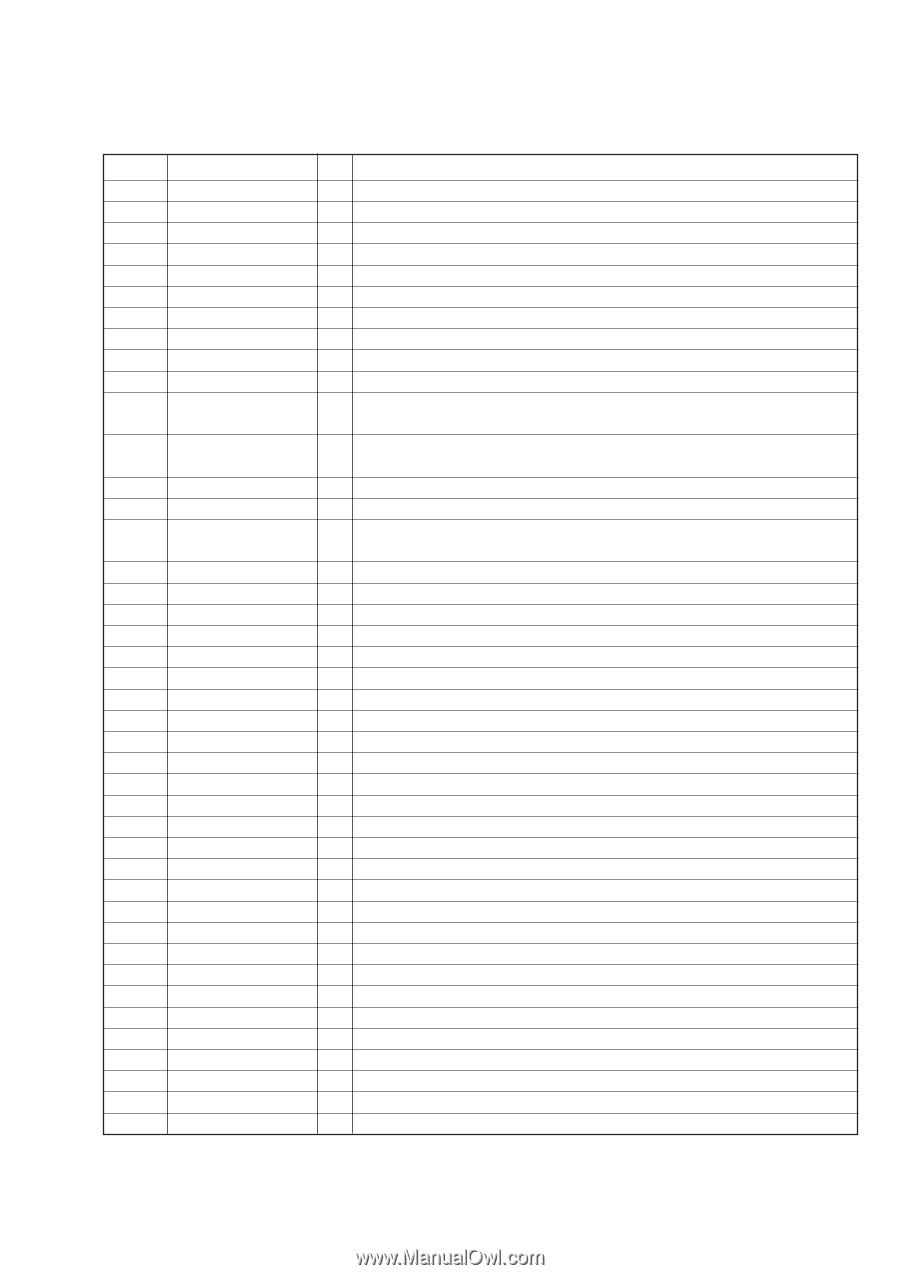

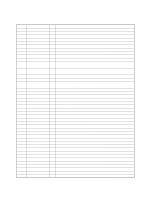

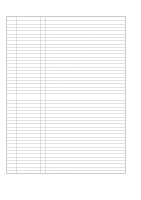

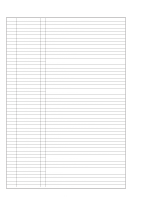

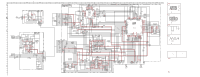

SECTION 6 DIAGRAMS 6-1. EXPLANATION OF IC TERMINALS IC503 DIGITAL SERVO, ATRAC (CXD2652AR) Pin No. Pin name I/O Description 1 MNT 0 2 MNT 1 3 MNT 2 4 MNT 3 5 SWDT 6 SCLK 7 XLAT 8 SRDT 9 SENS 10 XRST 11 SQSY 12 DQSY 13 WRPWR 14 NC 15 TX 16 17 18 19 20 21 22 23 24 25 26 27 28 29 - 39 40 41 42 43 44 45 46 - 49 50 51 52 53 54 55 OSC1 OSC0 XTSL NC RVSS DIN NC ADDT DATA ALRCK ABCK FS256 DVDD A00 - A08, A10, A11 DVSS XOE XCAS A09 XRAS XWE D0 - D3 MVCI ASYO ASYI AVDD BIAS RFI O Traverse count signal output. O Track jump detect output. - Not used (Open). - Not used (Open). I Inputs write data signal from system controller (IC801). I Inputs serial clock signal from system controller (IC801). I Inputs serial latch signal from system controller (IC801). O Outputs write data signal to system controller (IC801). O Outputs internal status (SENSE) to system controller (IC801). I Inputs reset signal from system controller (IC801). Reset : L O Output subcode Q sync (SCOR) to system controller (IC801). Outputs "L" every 13.3msec. Outputs "H" at all most mostly. O Outputs digital-in U-bit CD format subcode Q sync (SCOR) to system controller (IC801). Outputs "L" every 13.3msec. Outputs "H" at all most mostly. I Inputs laser power switching signal from system controller (IC801). - Not used (Open). I Input of write data taransmission timing from system controller (IC801). Also used as magnetic field head ON/OFF output. O Clock output (22.5MHz). I Clock input (22.5MHz). - Not used (Fixed at "L") - Not used (Ground). - Connect to ground. I Digital audio signal input pin (For optical input). - Not used (Open). I Audio data input from A/D converter (IC303). O Monitor/decode audio data output to A/D converter (IC303). O L/R clock output to D/A converter (IC303). O Bit clock signal output to A/D, D/A converter (IC303). O 11.2896MHz clock output (MCLK). - Power supply (+2.8V) for digital. O Address signal output to RAM (IC509). - Ground terminal. O Output enable contol signal output to RAM (IC509). O Column address strobe singal output to RAM (IC509). O Address signal output to RAM (IC509). O Row address strobe signal output to RAM (IC509). O Read/write control signal output to RAM (IC509). I Data signal input from RAM (IC509). - Not used (Connect to ground). O Playback EFM full-swing output (L : VSS, H : VDD). I Playback EFM asymmetry comparate voltage input. - Power supply (+2.8V) for analog. I Playback EFM asymmetry circuit constant current input. I Inputs playback EFM RF signal from RF amplifier (IC501). - 35 -