AMD AX2000DMT3C User Guide - Page 44

SYSCLK and SYSCLK# AC and DC Characteristics

|

View all AMD AX2000DMT3C manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 44 highlights

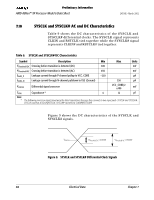

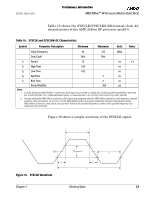

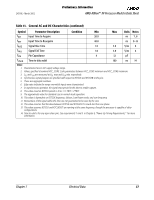

Preliminary Information AMD Athlon™ XP Processor Model 6 Data Sheet 24309E-March 2002 7.10 SYSCLK and SYSCLK# AC and DC Characteristics Table 9 shows the DC characteristics of the SYSCLK and SYSCLK# differential clocks. The SYSCLK signal represents CLKIN and RSTCLK tied together while the SYSCLK# signal represents CLKIN# and RSTCLK# tied together. Table 9. SYSCLK and SYSCLK# DC Characteristics Symbol Description Min Max Units VThreshold-DC Crossing before transition is detected (DC) 400 mV VThreshold-AC Crossing before transition is detected (AC) 450 mV ILEAK_P Leakage current through P-channel pullup to VCC_CORE -250 µA ILEAK_N Leakage current through N-channel pulldown to VSS (Ground) 250 µA VCROSS Differential signal crossover VCC_CORE/2 ±100 mV CPIN Capacitance * 4 12 pF Note: * The following processor inputs have twice the listed capacitance because they connect to two input pads-SYSCLK and SYSCLK#. SYSCLK connects to CLKIN/RSTCLK. SYSCLK# connects to CLKIN#/RSTCLK#. Figure 9 shows the DC characteristics of the SYSCLK and SYSCLK# signals. VCROSS VThreshold-DC = 400mV VThreshold-AC = 450mV Figure 9. SYSCLK and SYSCLK# Differential Clock Signals 32 Electrical Data Chapter 7