Compaq 8000 Technical Reference Guide: HP Compaq 8000 Elite Series Business De - Page 55

Parallel Interface Support, 4.1 Standard Parallel Port Mode, 4.3 Extended Capabilities Port Mode

|

UPC - 884420665106

View all Compaq 8000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 55 highlights

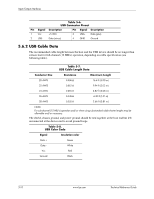

Input/Output Interfaces 5.4 Parallel Interface Support The SFF and CMT form factors include a system board header (J50) that supports an optional parallel bracket/cable assembly that provides a parallel interface for a peripheral device such as a printer. The parallel interface supports bi-directional 8-bit parallel data transfers with a peripheral device. The parallel interface supports three main modes of operation: ■ Standard Parallel Port (SPP) mode ■ Enhanced Parallel Port (EPP) mode ■ Extended Capabilities Port (ECP) mode These three modes (and their submodes) provide complete support as specified for an IEEE 1284 parallel port. 5.4.1 Standard Parallel Port Mode The Standard Parallel Port (SPP) mode uses software-based protocol and includes two sub-modes of operation, compatible and extended, both of which can provide data transfers up to 150 KB/s. In the compatible mode, CPU write data is simply presented on the eight data lines. A CPU read of the parallel port yields the last data byte that was written. 5.4.2 Enhanced Parallel Port Mode In Enhanced Parallel Port (EPP) mode, increased data transfers are possible (up to 2 MB/s) due to a hardware protocol that provides automatic address and strobe generation. EPP revisions 1.7 and 1.9 are both supported. For the parallel interface to be initialized for EPP mode, a negotiation phase is entered to detect whether or not the connected peripheral is compatible with EPP mode. If compatible, then EPP mode can be used. In EPP mode, system timing is closely coupled to EPP timing. A watchdog timer is used to prevent system lockup. 5.4.3 Extended Capabilities Port Mode The Extended Capabilities Port (ECP) mode, like EPP, also uses a hardware protocol-based design that supports transfers up to 2 MB/s. Automatic generation of addresses and strobes as well as Run Length Encoding (RLE) decompression is supported by ECP mode. The ECP mode includes a bi-directional FIFO buffer that can be accessed by the CPU using DMA or programmed I/O. For the parallel interface to be initialized for ECP mode, a negotiation phase is entered to detect whether or not the connected peripheral is compatible with ECP mode. If compatible, then ECP mode can be used. The ECP mode includes several sub-modes as determined by the Extended Control register. Two submodes of ECP allow the parallel port to be controlled by software. In these modes, the FIFO is cleared and not used, and DMA and RLE are inhibited. Technical Reference Guide www.hp.com 5-5